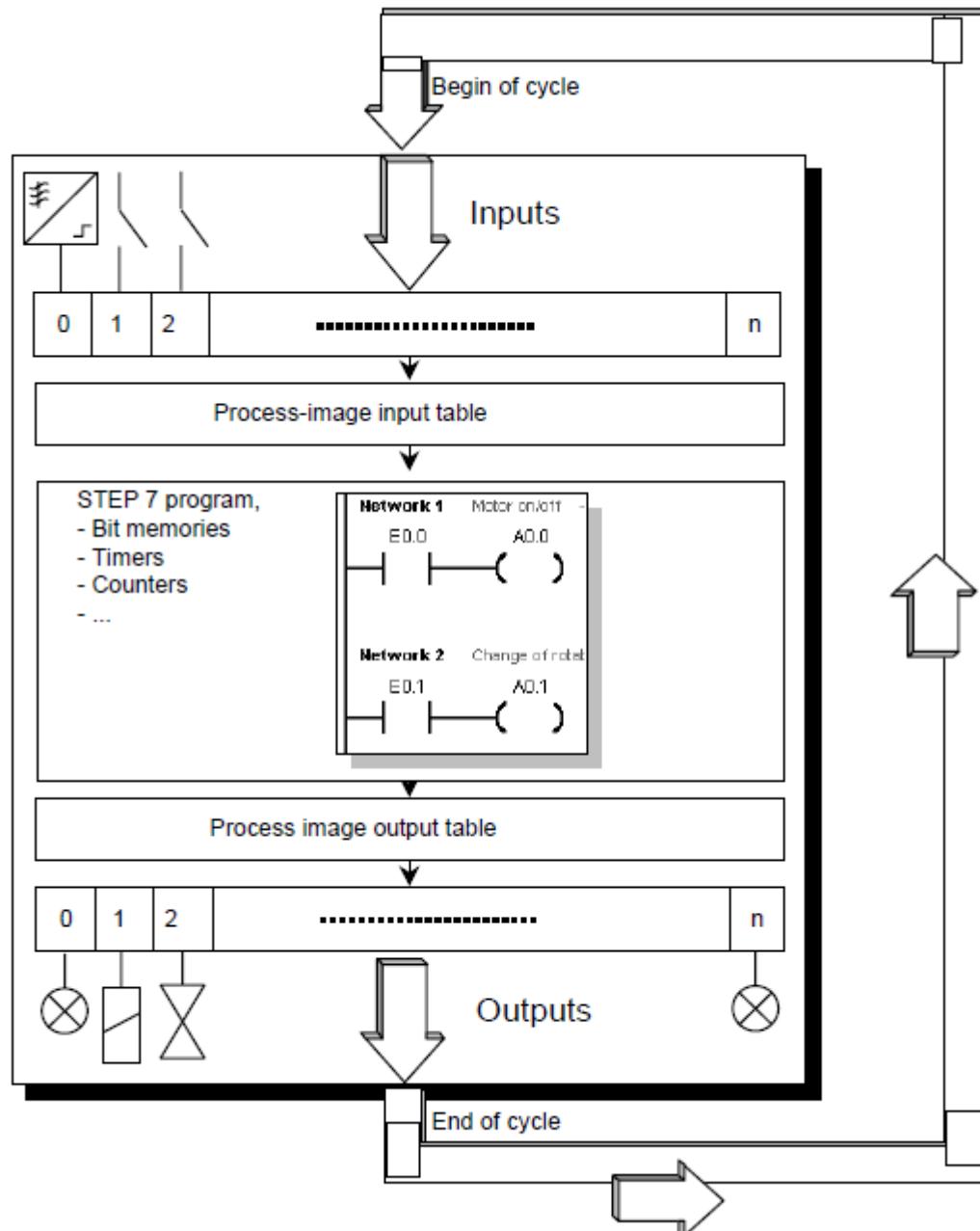

# Lógica de Controle

# CLPs

## Vantagens do uso de Controladores Lógicos Programáveis

- Ocupam menor espaço;

- Requerem menor potência elétrica;

- Podem ser reutilizados;

- São programáveis, permitindo alterar os parâmetros de controle;

- Apresentam maior confiabilidade;

- Manutenção mais fácil e rápida;

- Oferecem maior flexibilidade;

- Apresentam interface de comunicação com outros CLP's e computadores de controle;

- Permitem maior rapidez na elaboração do projeto do sistema.

# Arquitetura do CLP

# CPU

INSTITUTO FEDERAL

SANTA CATARINA

Campus Araranguá

# CPU

# Memória

| <i>Tipo de Memória</i> | <i>Descrição</i>                                 | <i>Observação</i>                                                                       |

|------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------|

| <b>RAM DINÂMICA</b>    | Memória de acesso aleatório                      | - Volátil<br>- Gravada pelo usuário<br>- Lenta<br>- Ocupa pouco espaço<br>- Menor custo |

| <b>RAM</b>             | Memória de acesso aleatório                      | - Volátil<br>- Gravada pelo usuário<br>- Rápida<br>- Ocupa mais espaço<br>- Maior custo |

| <b>ROM MÁSCARA</b>     | Memória somente de leitura                       | - Não Volátil<br>- Não permite apagamento<br>- Gravada pelo fabricante                  |

| <b>PROM</b>            | Memória programável somente de leitura           | - Não volátil<br>- Não permite apagamento<br>- Gravada pelo usuário                     |

| <b>EPROM</b>           | Memória programável/ apagável somente de leitura | - Não Volátil<br>- Apagamento por ultravioleta<br>- Gravada pelo usuário                |

| <b>EEPROM</b>          | Memória programável/ apagável somente de leitura | - Não Volátil<br>- Apagável eletricamente                                               |

| <b>FLASH EPROM</b>     | Memória programável/ apagável somente de leitura | - Gravada pelo usuário                                                                  |

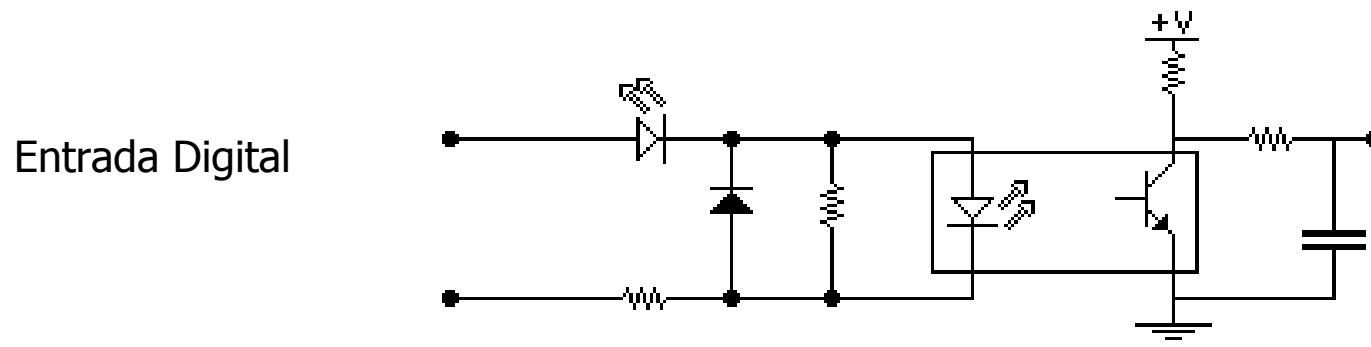

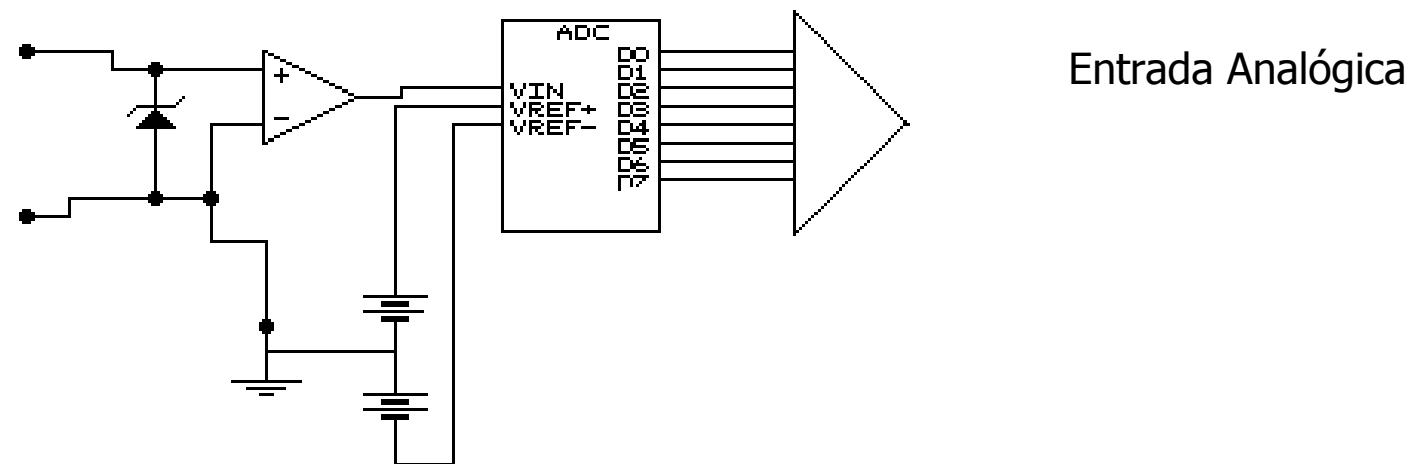

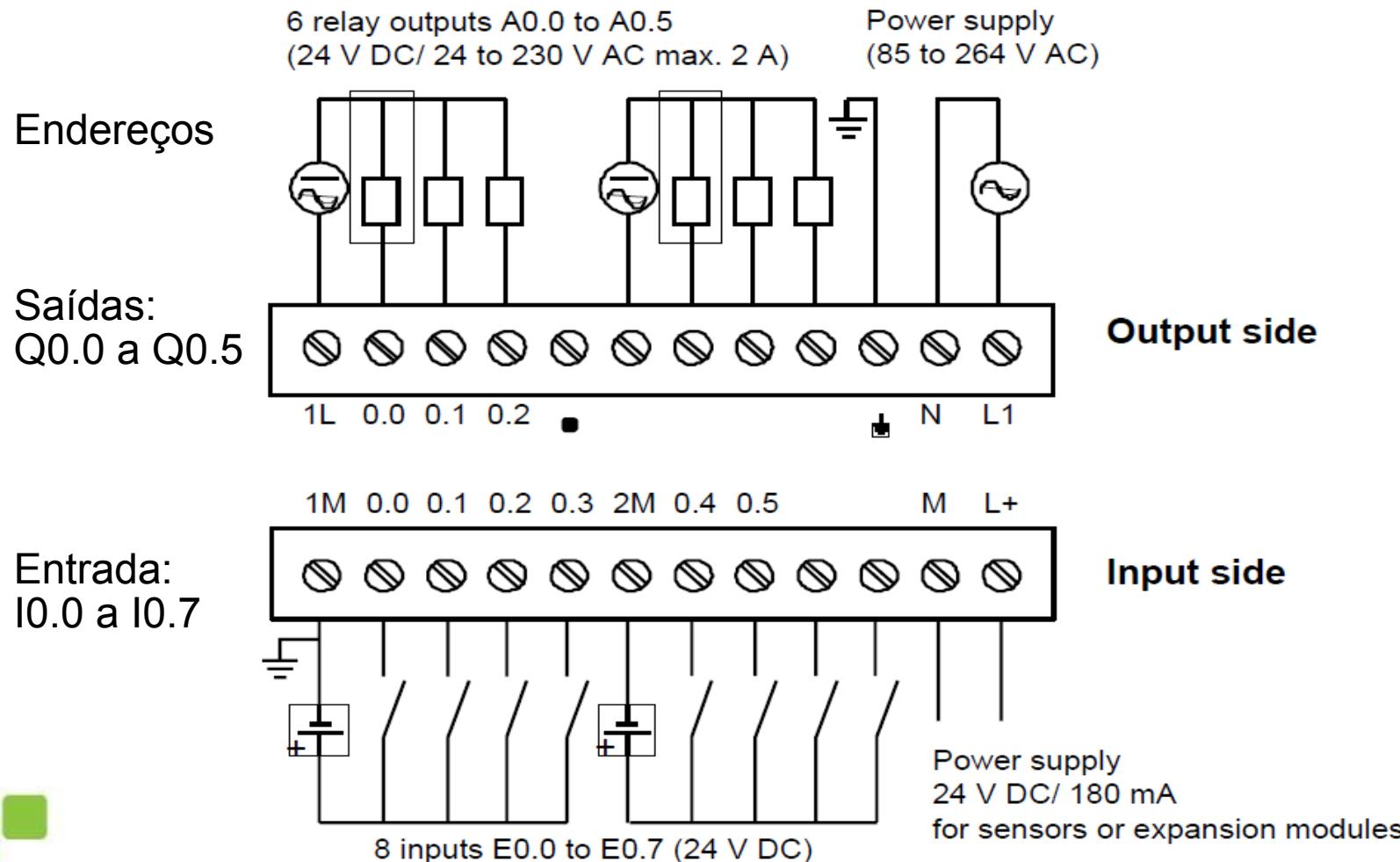

# Entradas

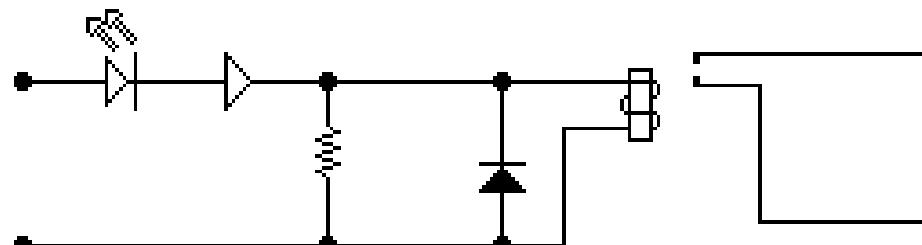

Entrada Digital

Entrada Analógica

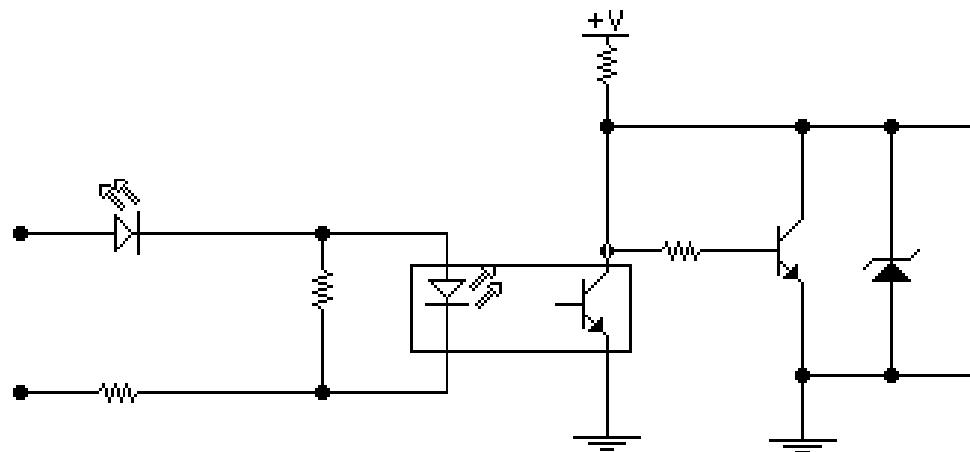

# Saídas

Saída Digital

à Relê

Saída Digital

à Transistor

INSTITUTO FEDERAL

SANTA CATARINA

Campus Araranguá

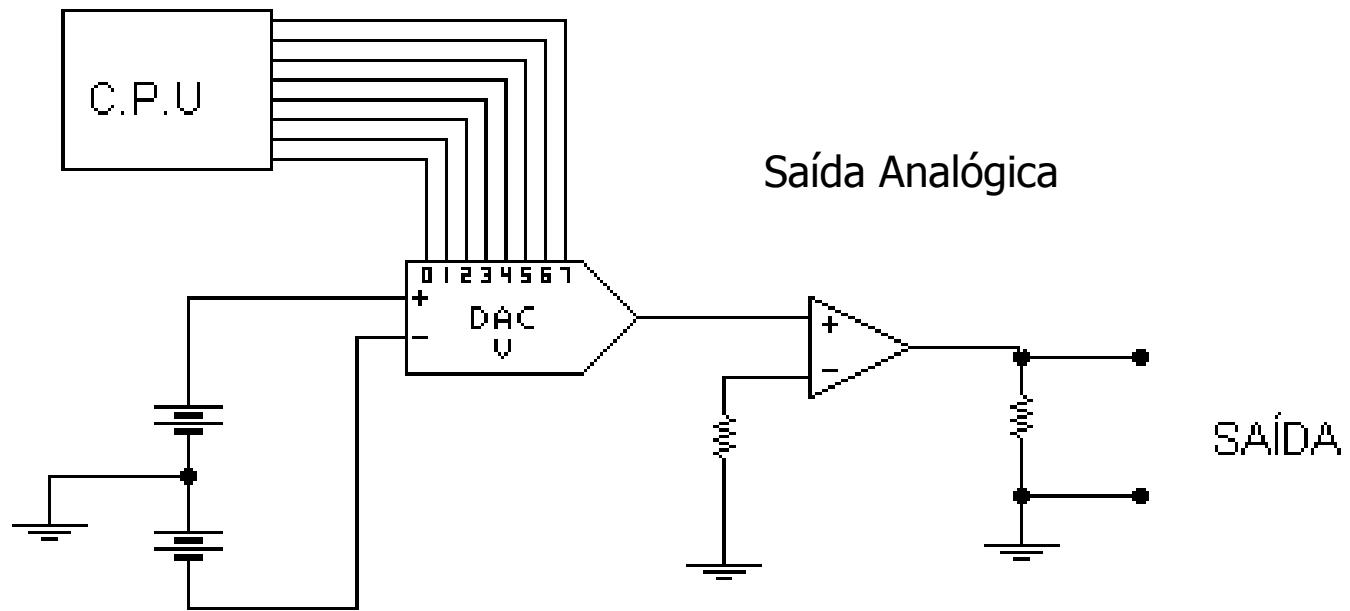

# Saídas

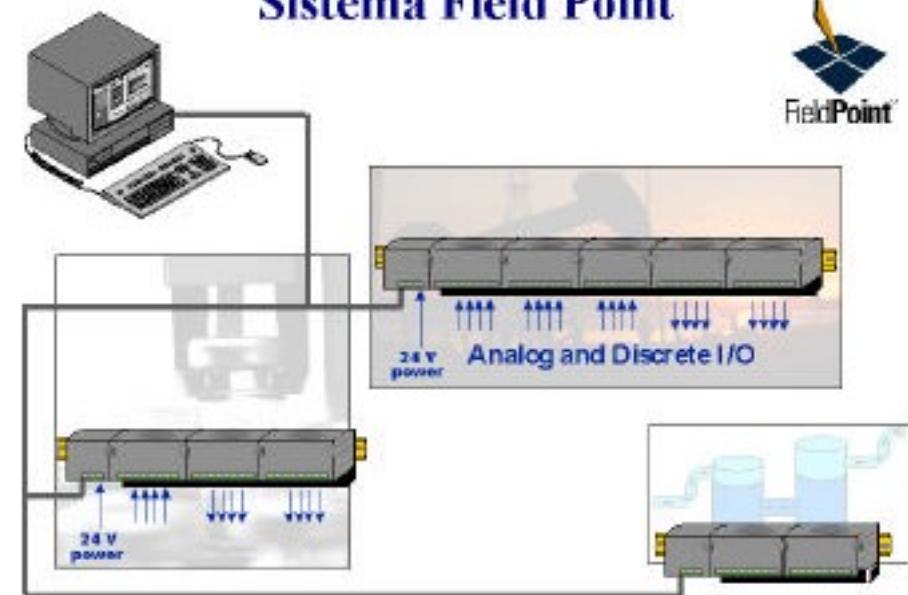

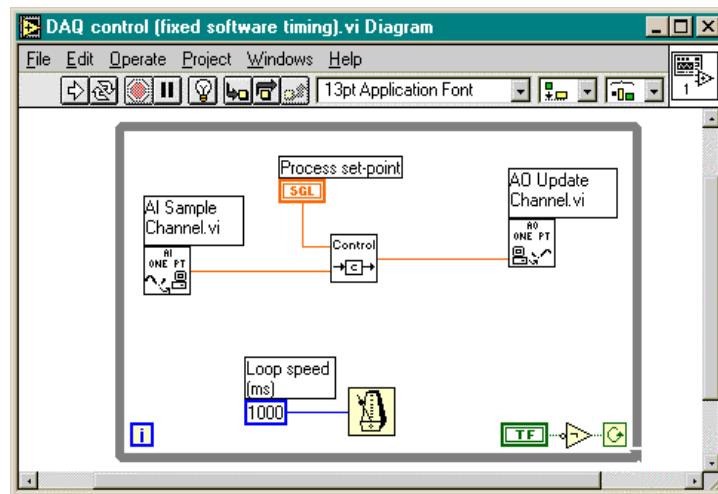

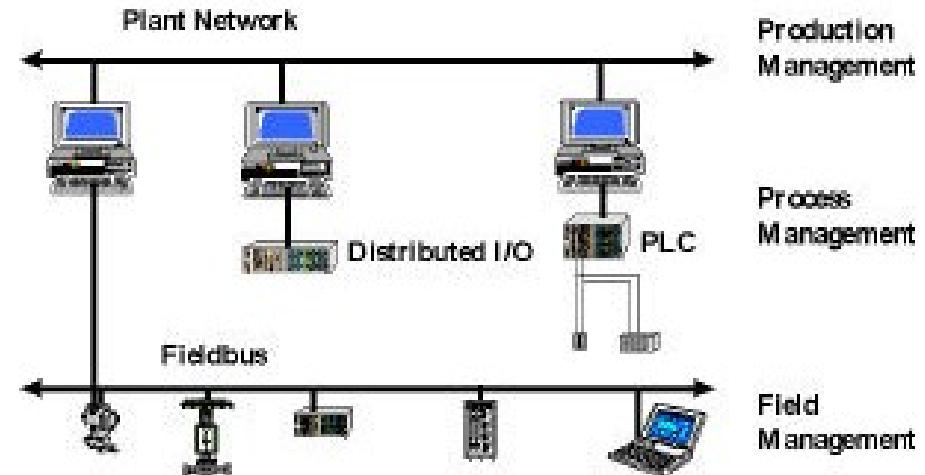

# Tecnologias Industriais

Sistema Field Point

# Tecnologias Industriais

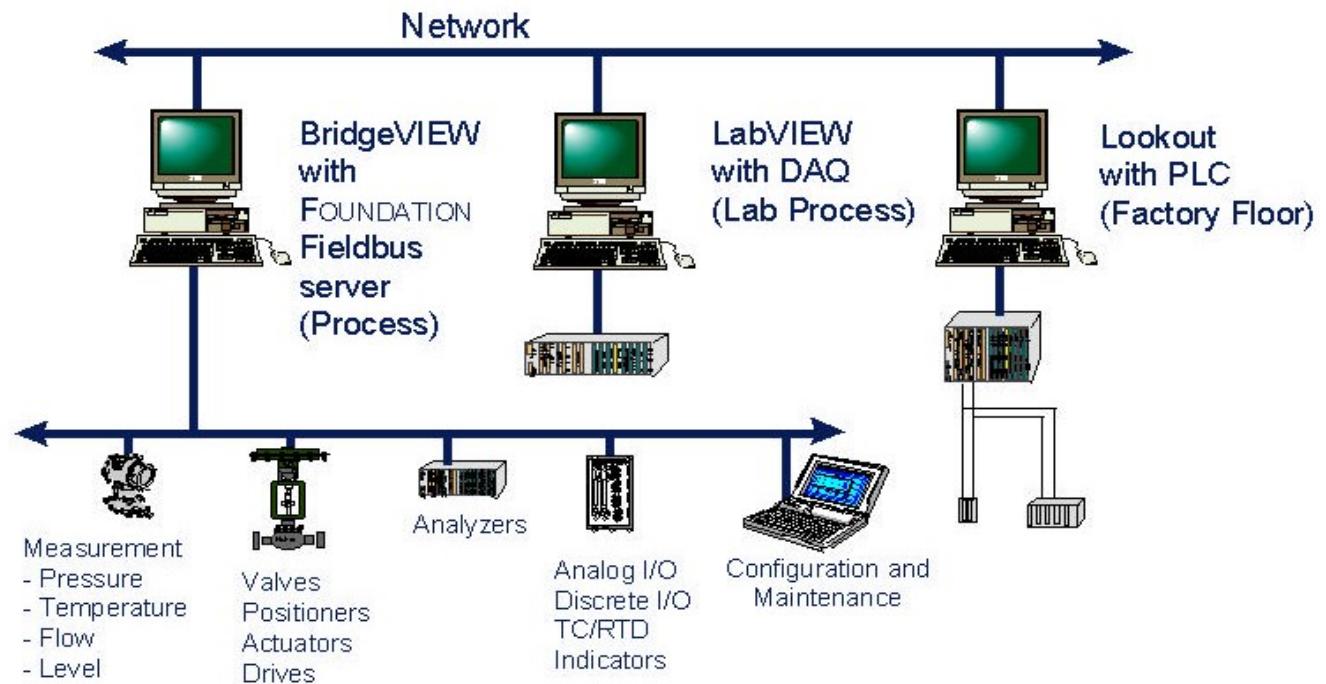

## Arquitetura BridgeVIEW

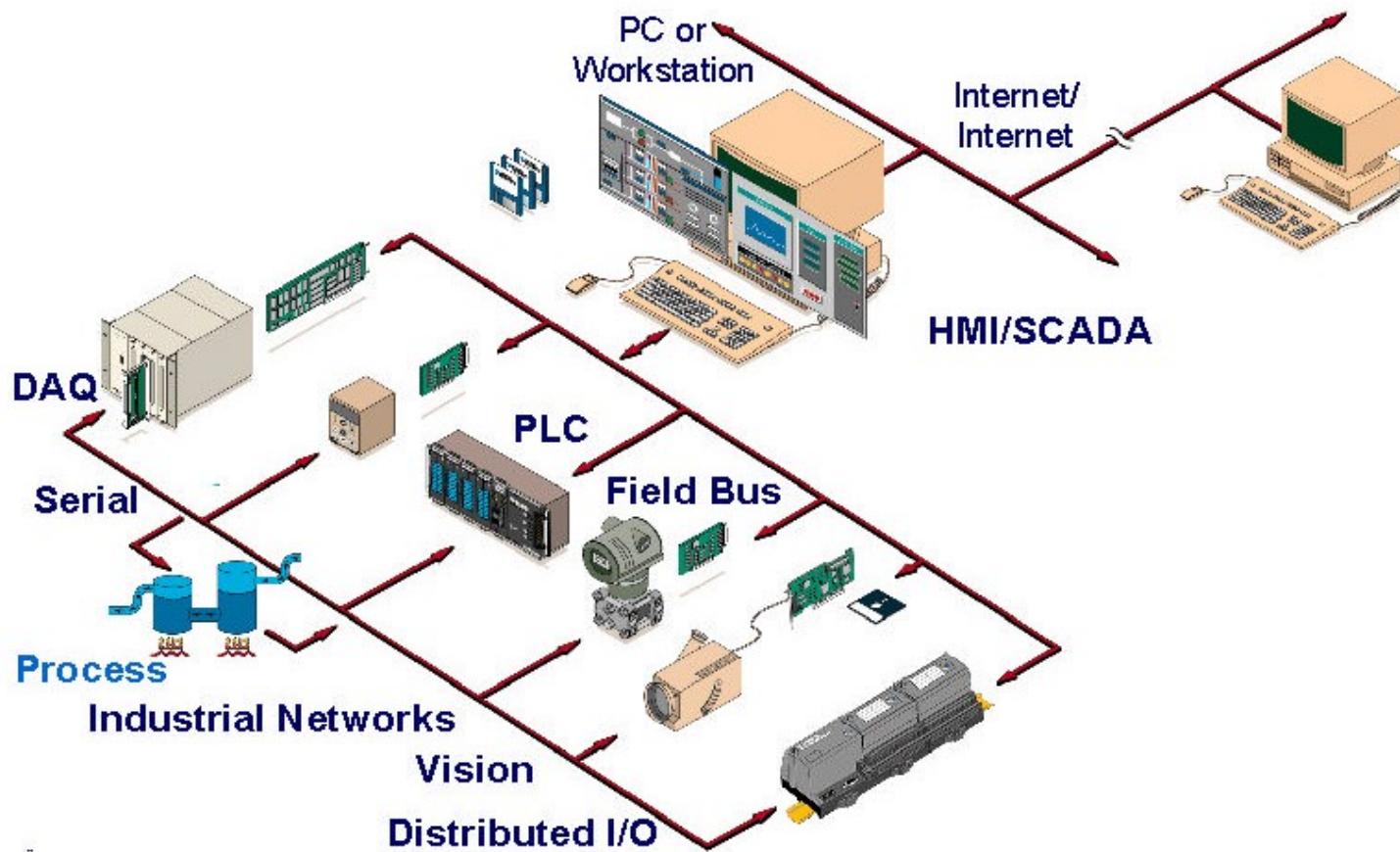

# Tecnologias Industriais

## Aplicações de Automação

# Tecnologias Industriais

# CLPs Comerciais

Pequeno Porte (Micro CLP)

Até 320 E/S

CLP de Médio Porte

Até 2500 E/S

CLP de Grande Porte

Até 5000 E/S

# CLPs Comerciais

OMRON

Rockwell

Automation

SIEMENS

AB

Allen-Bradley

Rexroth

Bosch Group

BOSCH

Schneider

Electric

altus

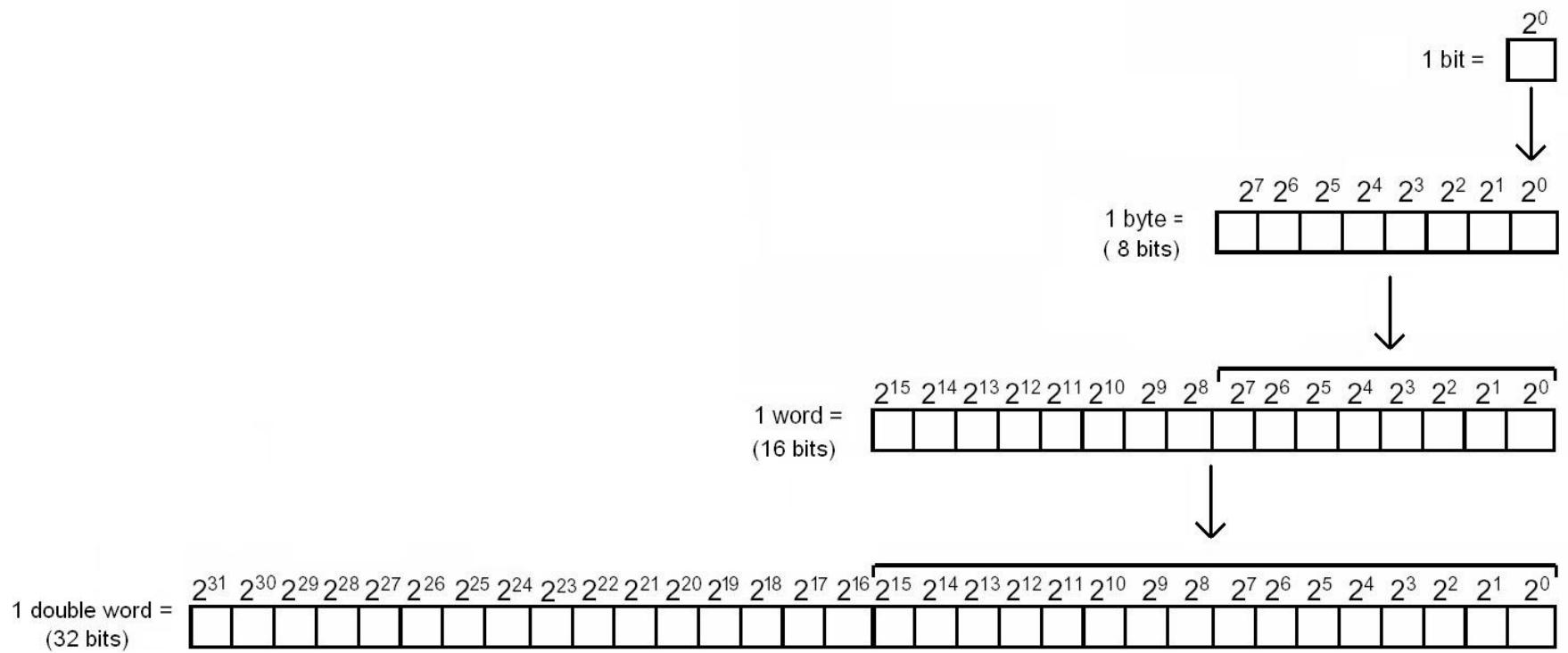

# Estrutura de Dados

INSTITUTO FEDERAL

SANTA CATARINA

Campus Araranguá

# Estrutura de Dados

# Estrutura de Dados

| Representation                        | Byte (B)              | Word (W)              | Double Word (D)                                                                        |

|---------------------------------------|-----------------------|-----------------------|----------------------------------------------------------------------------------------|

| Unsigned Integer                      | 0 to 255              | 0 to 65,535           | 0 to 4,294,967,295                                                                     |

|                                       | 0 to FF               | 0 to FFFF             | 0 to FFFF FFFF                                                                         |

| Signed Integer                        | -128 to +127          | -32,768 to +32,767    | -2,147,483,648 to +2,147,483,647                                                       |

|                                       | 80 to 7F              | 8000 to 7FFF          | 8000 0000 to 7FFF FFFF                                                                 |

| Real<br>IEEE 32-bit<br>Floating Point | <i>Not applicable</i> | <i>Not applicable</i> | +1.175495E-38 to +3.402823E+38 (positive)<br>-1.175495E-38 to -3.402823E+38 (negative) |

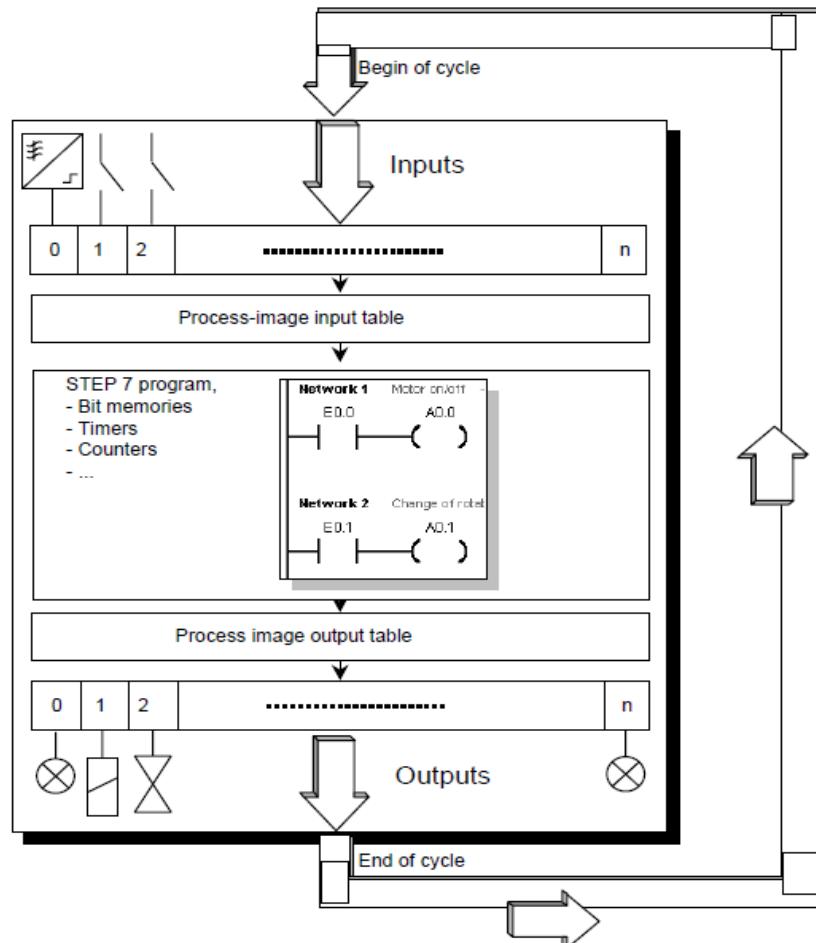

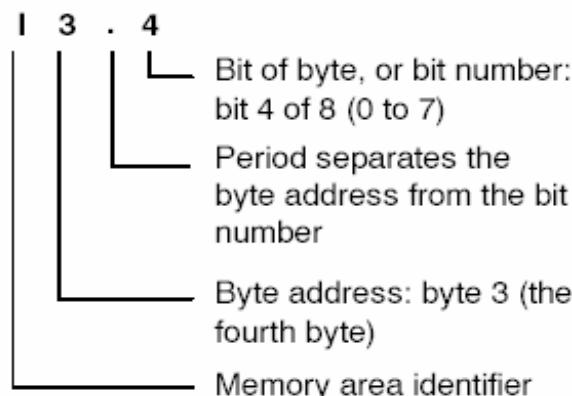

To access a bit in a memory area, you specify the address, which includes the memory area identifier, the byte address, and the bit number. Figure 4-3 shows an example of accessing a bit (which is also called “byte.bit” addressing). In this example, the memory area and byte address (I = input, and 3 = byte 3) are followed by a period (“.”) to separate the bit address (bit 4).

Process-image Input (I) Memory Area

|        |   |   |   |   |   |   |   |

|--------|---|---|---|---|---|---|---|

| 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Byte 0 |   |   |   |   |   |   |   |

| Byte 1 |   |   |   |   |   |   |   |

| Byte 2 |   |   |   |   |   |   |   |

| Byte 3 |   |   |   |   |   |   |   |

| Byte 4 |   |   |   |   |   |   |   |

| Byte 5 |   |   |   |   |   |   |   |

# Estrutura de Dados

- **TIPOS DE ENDEREÇOS**

- **I** = DIGITAL INPUT

- **Q** = DIGITAL OUTPUT (QUIT)

- **AIW** = ANALOG INPUT

- **AQW** = ANALOG OUTPUT (QUIT)

- **V** = VARIABLE (FLAG)

- **M** = MEMORY

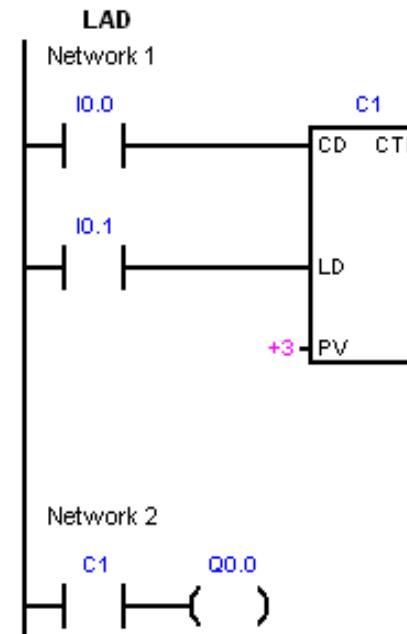

- **C** = COUNTER

- **T** = TIMER

# Estrutura de Dados

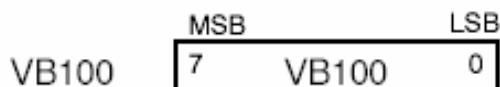

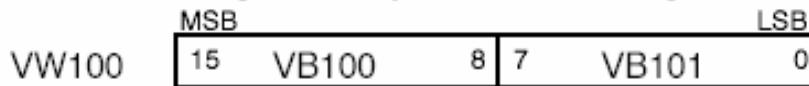

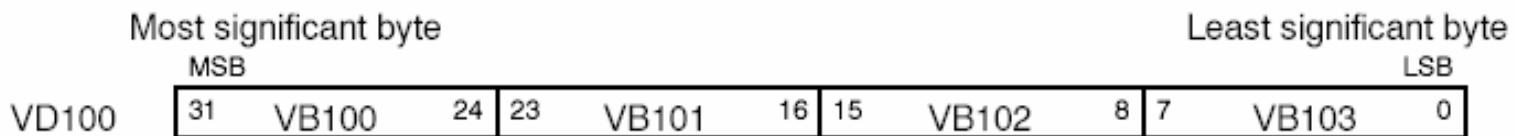

V B 100

Byte address

Access to a byte size

Area identifier

V W 100

Byte address

Access to a word size

Area identifier

V D 100

Byte address

Access to a double word size

Area identifier

Most significant byte

Least significant byte

MSB = most significant bit

LSB = least significant bit

Figure 4-4 Comparing Byte, Word, and Double-Word Access to the Same Address

# Estrutura de Dados

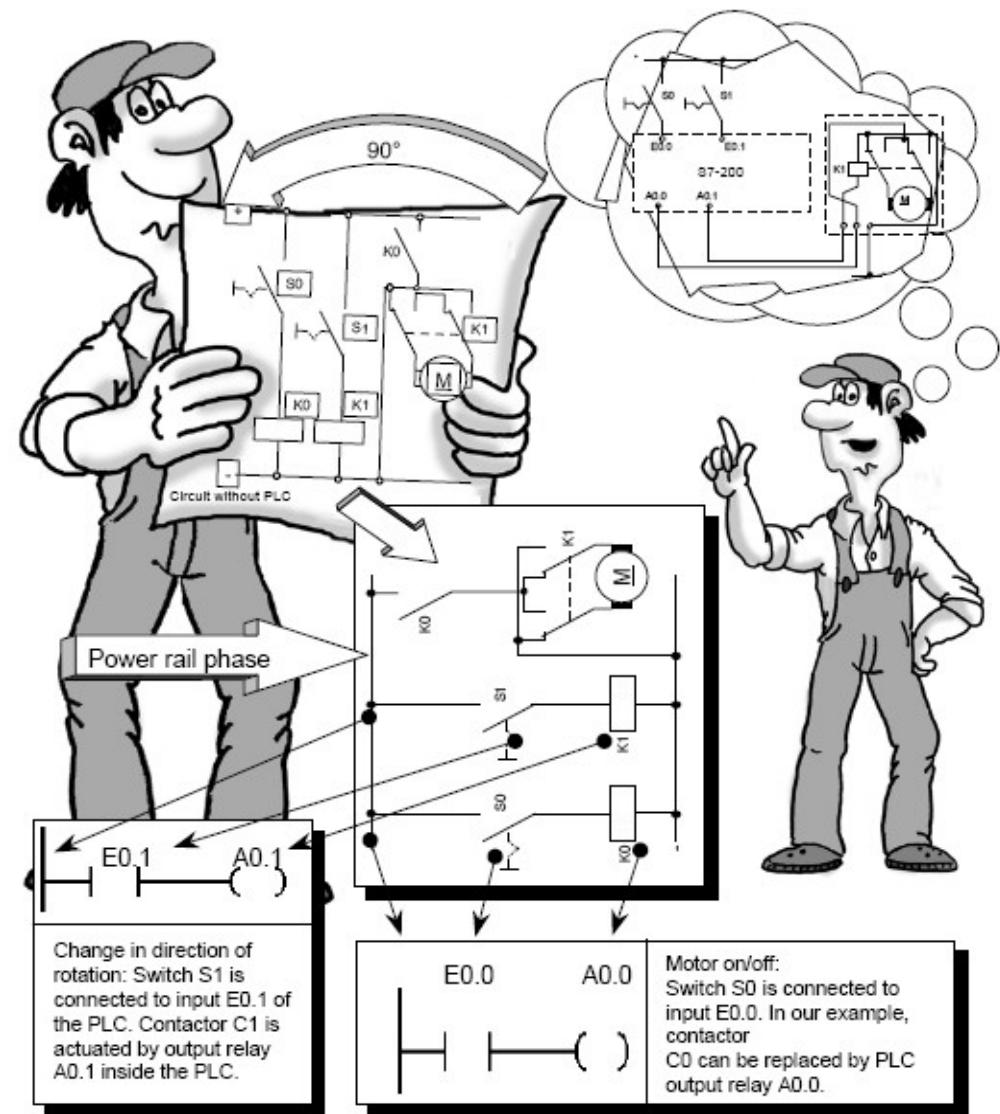

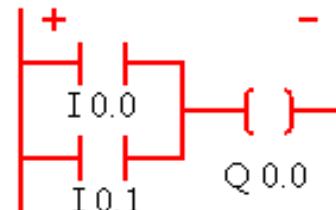

# Linguagem Ladder

| Contactor | Instruction on the PLC/<br>corresponding function                                                                          |

|-----------|----------------------------------------------------------------------------------------------------------------------------|

|           | Scan:<br>Is current flowing ?<br>If yes, then the result<br>of the scan is true.<br>(Result is "1")                        |

|           | Scan:<br>Is <u>no</u> current flowing ?<br>If yes (no current), then the<br>result of the scan is true.<br>(Result is "0") |

|           | Coil:<br>If the value "true" (current) is<br>passed to a coil<br>it is activated<br>(The coil starts up).                  |

|           | Series circuit:<br>(AND logic).<br>The first switch AND the<br>second switch must be closed<br>in order to pass current.   |

|           | Parallel circuit<br>(OR logic).<br>The first switch OR the<br>second switch must be closed<br>in order to pass current.    |

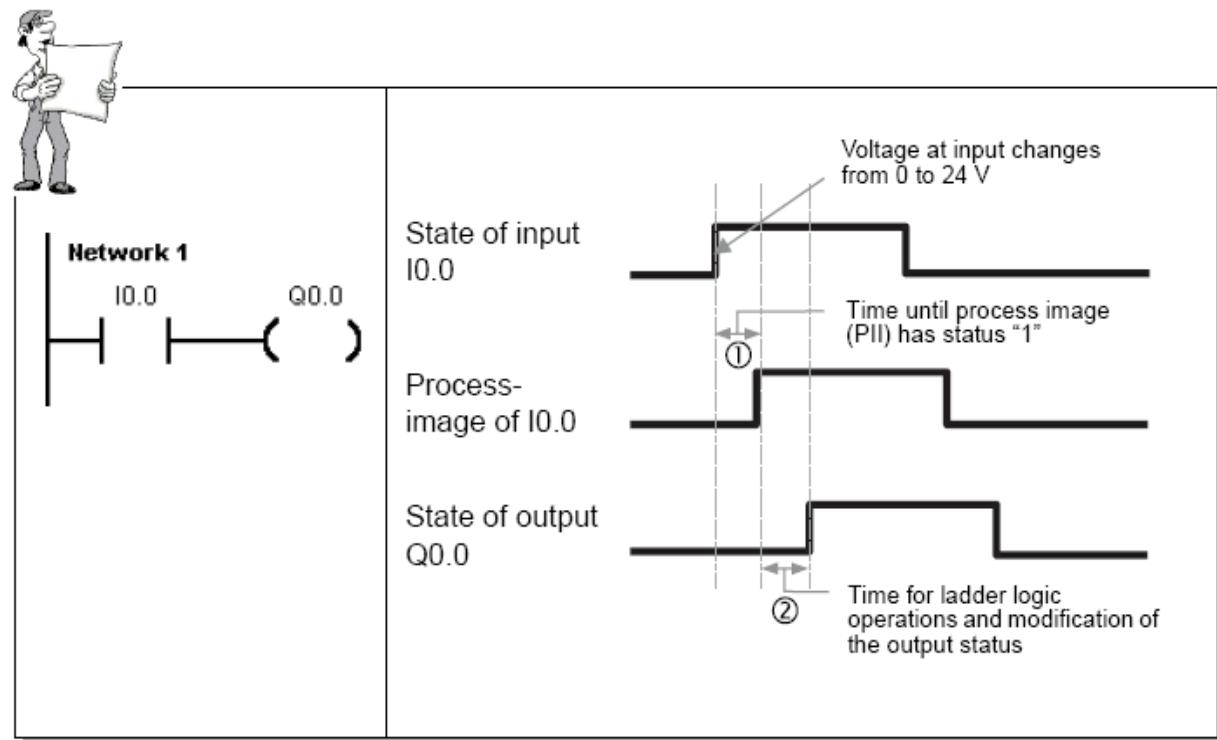

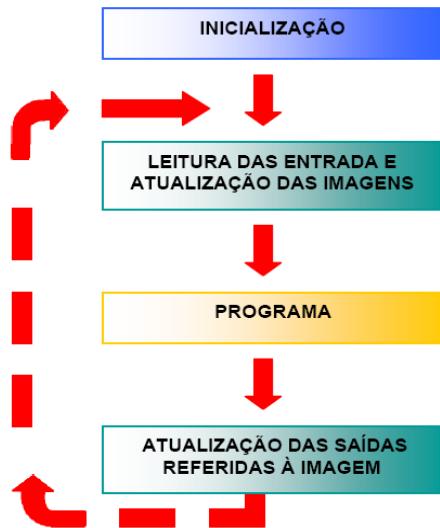

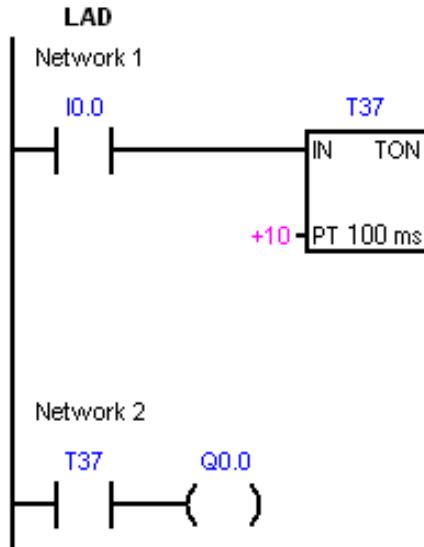

# Linguagem Ladder

# Linguagem Ladder

# Linguagem Ladder

# Linguagem Ladder

- definição da função lógica a ser programada

- transformação desta função em programa assimilável pelo CLP

- implementação física do controlador e de suas interfaces com o processo

# Linguagem Ladder

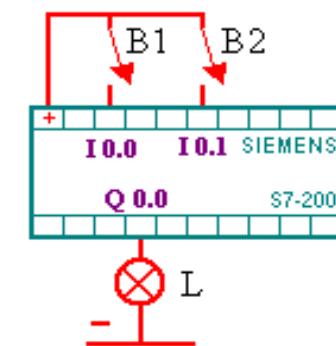

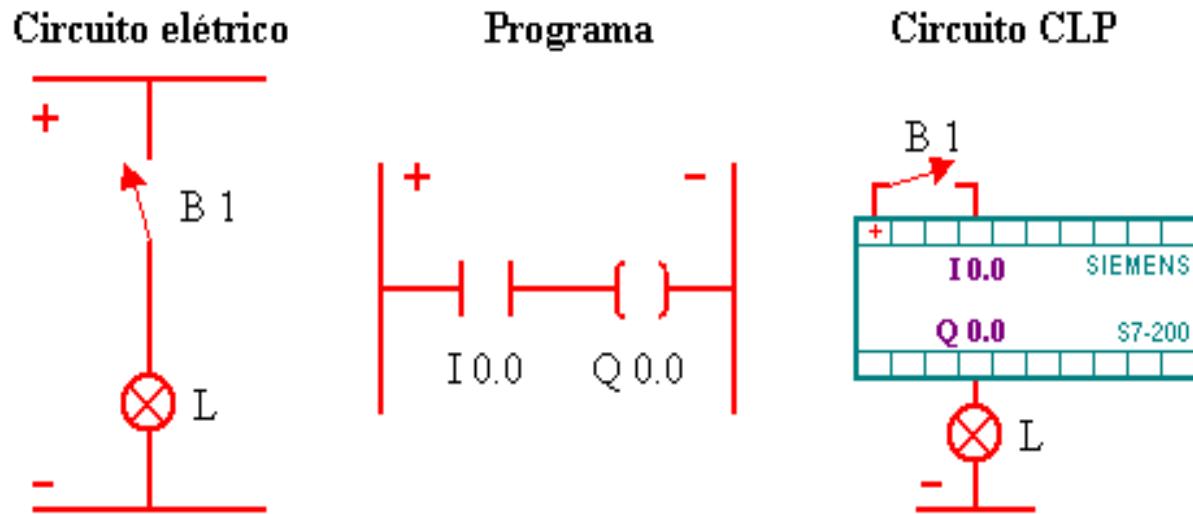

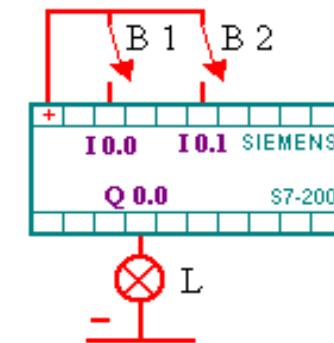

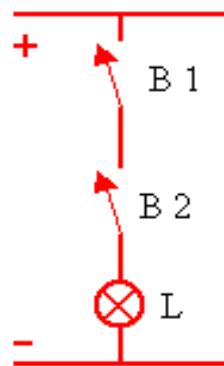

Círcuito elétrico

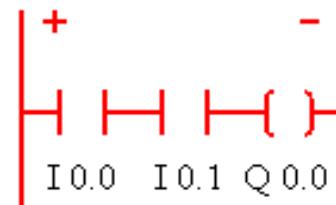

Programa

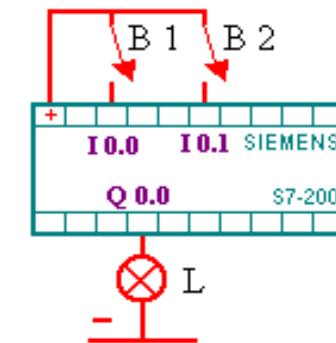

Círcuito CLP

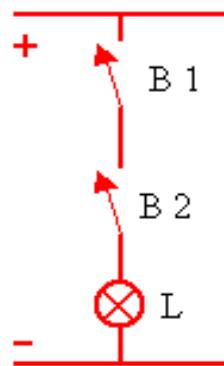

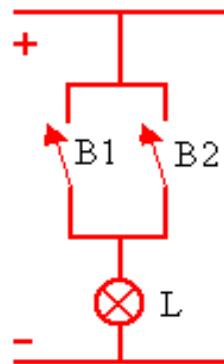

Círcuito elétrico

Programa

Círcuito CLP

# Linguagem Ladder

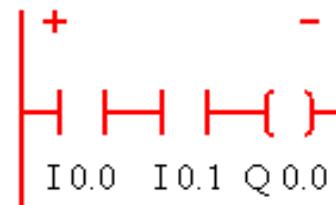

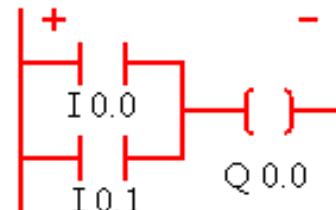

Círcuito elétrico

Programa

Círcuito CLP

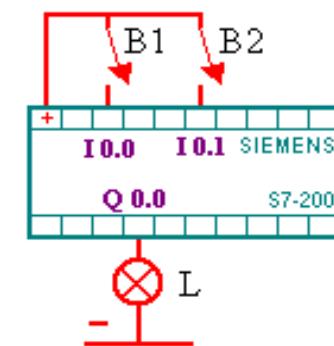

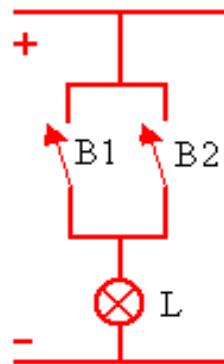

Círcuito elétrico

Programa

Círcuito CLP