AULA 15 - Microprocessadores - Graduação: mudanças entre as edições

imported>Fargoud Sem resumo de edição |

imported>Fargoud |

||

| (34 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 6: | Linha 6: | ||

* Áreas de atuação: | * Áreas de atuação: | ||

** Desenvolvimento de novos modelos de computação | ** Desenvolvimento de novos modelos de computação | ||

** Desenvolvimento de novas arquiteturas de sistemas computacionais (processadores multi-core, multiprocessadores, sistemas de cluster, grid e cloud computing) | ** Desenvolvimento de novas arquiteturas de sistemas computacionais (processadores multi-core, multiprocessadores, sistemas de cluster, grid e cloud computing) | ||

** Viabiliza novas aplicações computacionais (modelos matemáticos): | ** Viabiliza novas aplicações computacionais (modelos matemáticos): | ||

| Linha 26: | Linha 23: | ||

Em uma das linhas de pesquisa, ao invés de se pensar em um único processador com características superiores, os desenvolvedores começaram a seguir a abordagem de utilizar vários sub-sistemas de processamento acoplados, ou seja, por meio da estratégia "dividir para conquistar". | Em uma das linhas de pesquisa, ao invés de se pensar em um único processador com características superiores, os desenvolvedores começaram a seguir a abordagem de utilizar vários sub-sistemas de processamento acoplados, ou seja, por meio da estratégia "dividir para conquistar". | ||

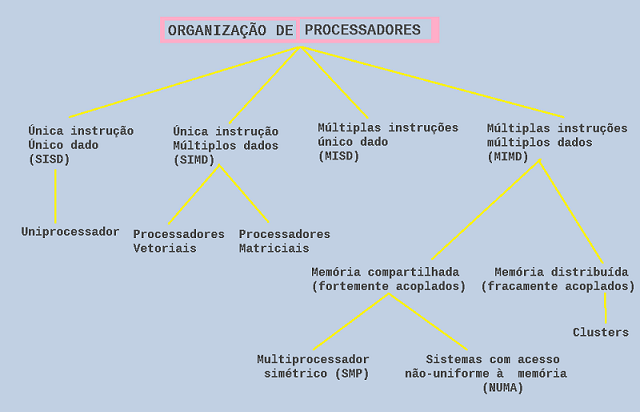

=Tipos de sistemas com processadores paralelos= | |||

Taxonomia proposta por Flymm (1972): | |||

[[image: MIPparal1.png|center]] | [[image: MIPparal1.png|center]] | ||

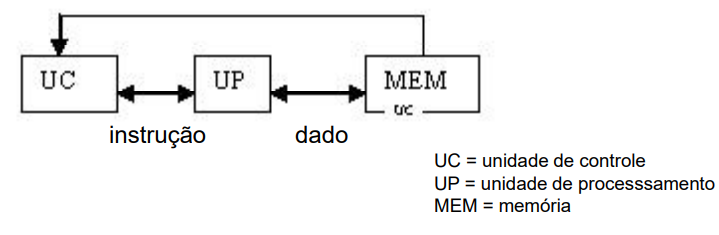

==Única instrução, único dado (SISD - ''single instruction, single data'')== | |||

Um único processador executa uma única sequência de instruções, usando dados armazenados em uma única memória. | |||

'''Exemplo:''' Máquina de Von Neumann | |||

[[image: MIPparal2.png|center]] | |||

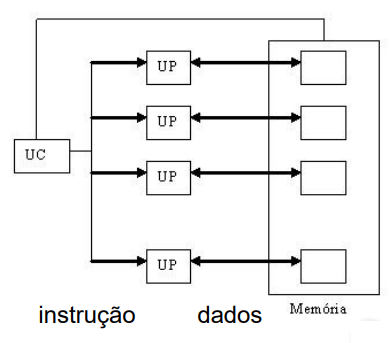

==Única instrução, múltiplos dados (SIMSD - ''single instruction, multiple data'')== | |||

Nestes computadores, ocorre a execução síncrona da instrução, para todos os dados. | |||

Uma única instrução de máquina controla a execução simultânea de um certo número de elementos de processamento, em passos de execução. | |||

Cada elemento de processamento tem uma memória de dados a ele associada, de modo que cada instrução é executada sobre um conjunto de dados diferente em cada processador. | |||

Os processadores vetoriais e matriciais pertencem a essa categoria. | |||

[[image: MIPparal3.png|center]] | |||

=Arquiteturas de | '''Exemplos:''' | ||

* Processadores vetoriais ([https://adrenaline.uol.com.br/forum/threads/cray-1-o-primeiro-supercomputador-da-historia.189297/ Cray 1]) | |||

* [https://blogs.nvidia.com/blog/2009/12/16/whats-the-difference-between-a-cpu-and-a-gpu/ GPU] - ou ''graphics processing unit'', [https://blogs.nvidia.com/blog/2009/12/16/whats-the-difference-between-a-cpu-and-a-gpu/ Unidade Gráfica de Processamento] | |||

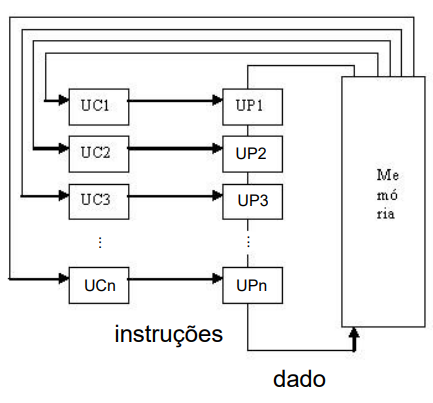

==Múltiplas instruções, único dado (MISD - ''multiple instruction, single data'')== | |||

Uma sequência de dados é transmitida para um conjunto de processadores, cada um dos quais executa uma sequência de instruções diferente. | |||

Isto é, várias instruções são executadas em um único fluxo de dados. | |||

Essa estrutura nunca foi implementada. | |||

[[image: MIPparal4.png|center]] | |||

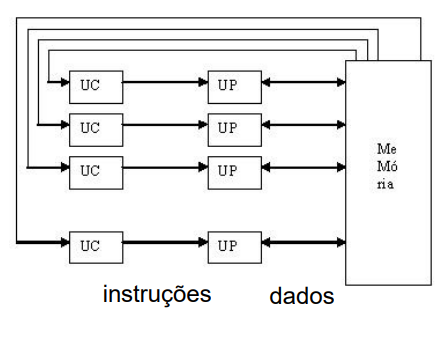

==Múltiplas instruções, múltiplos dados (MIMD - ''multiple instruction, multiple data'')== | |||

Permite a execução de instruções diferentes para cada um dos dados. | |||

Ou seja, um conjunto de processadores executa simultaneamente sequências diferentes de instruções, sobre conjuntos de dados distintos. | |||

Os SMPs, clusters e sistemas NUMA pertencem a esta categoria. | |||

'''Exemplos:''' | |||

* Arquiteturas paralelas atuais | |||

* [https://www.top500.org/ Top500.org] | |||

[[image: MIPparal5.png|center]] | |||

Em uma organização MIMD, os processadores são de propósito geral; cada um pode processar todas as instruções necessárias para realizar a transformação de dados apropriada. | |||

=Outras classificações para Paralelismo= | |||

Há várias fontes de execução paralela em um computador moderno. | |||

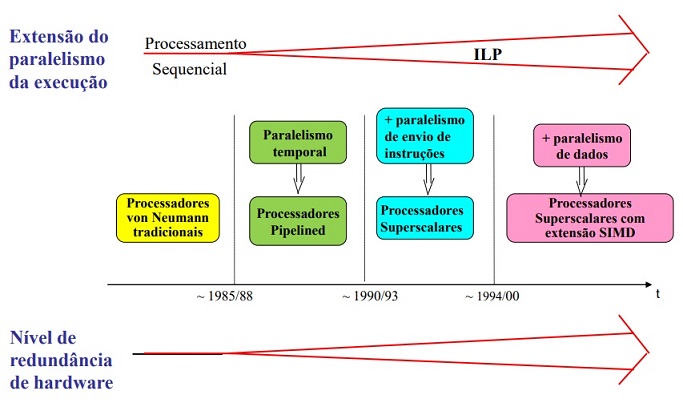

==Paralelismo no Nível de Instrução (ILP)== | |||

Permite executar várias instruções em cada ciclo de relógio. | |||

Modificações na microarquitetura do processador para possibilitar a execução paralela de instruções. | |||

Abordagens: | |||

* Paralelismo temporal: encadeamento no fluxo de execução das instruções (pipeline); | |||

* Paralelismo na emissão de instruções: submissão de várias instruções para execução pelo fluxo de dados (VLIW - ''very long instruction line'' (128 bits) e superescalaridade); | |||

* Paralelismo de dados: permite executar várias instâncias da mesma instrução para um conjunto de dados (processamento SIMD ou vetorial). | |||

[[image: MIPparalel6.png|center]] | |||

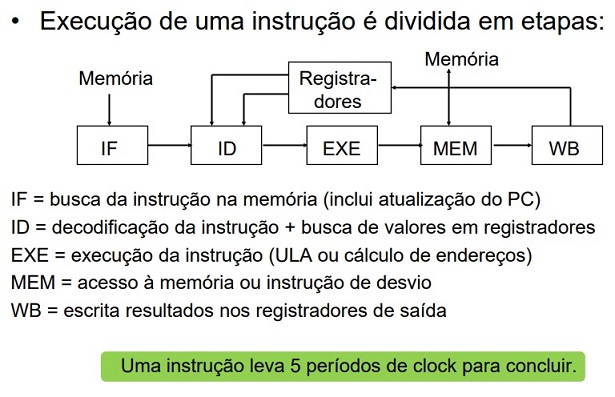

==Pipelining== | |||

[[image: MIPparalel7.png|center]] | |||

[[image: | [[image: MIPparalel8.png|center]] | ||

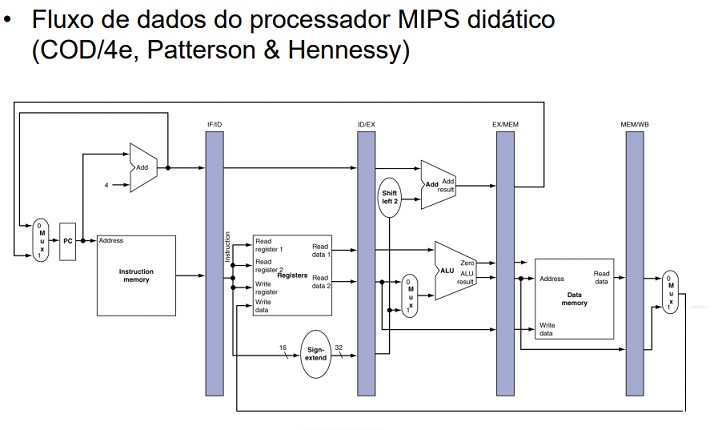

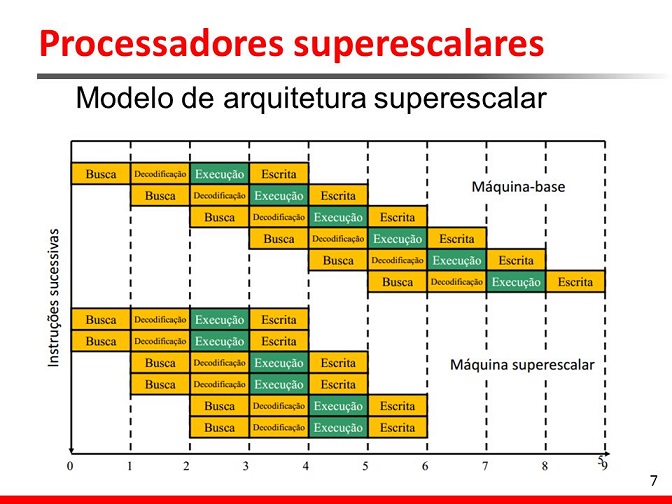

=Arquiteturas de processador Superescalares= | |||

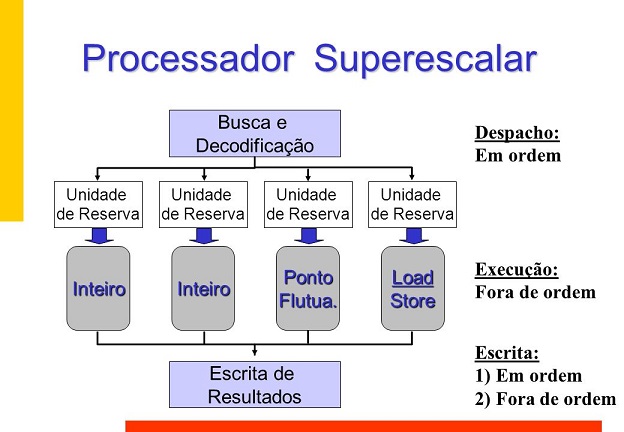

Processadores Superescalares são todos os que possuem mais de uma unidade funcional em cada ''pipeline'', as quais permitem a execução de mais de uma instrução simultaneamente (no mesmo ciclo de ''clock''). | |||

A arquitetura pipeline já permite que diversas instruções sejam executadas ao mesmo tempo, desde que estejam em '''estágios diferentes do pipeline'''. | |||

Porém, ainda que várias instruções sejam executadas concorrentemente (em cada estágio do pipeline), apenas uma instrução encontra-se na fase de execução, ou seja, o sistema continua sendo SISD. | |||

[[image: MIPprocpipelined.png|center]] | |||

Já na arquitetura superescalar, várias instruções podem ser iniciadas simultaneamente e executadas independentemente umas das outras. | |||

A partir do Pentium, a maioria dos processadores para computadores pessoais atualmente são superescalares. | |||

Isto é obtido através da implementação de '''múltiplas unidades funcionais''', que são unidades onde as instruções são executadas. | |||

[[image: MIPprocsuperesc.png|center]] | |||

O Pentium, por exemplo, trabalha internamente '''como se fosse composto por dois processadores de 32 bits distintos''' (chamados de ''pipeline U'' e ''pipeline V''), sendo capaz de processar duas instruções por ciclo de clock (uma em cada pipeline). | |||

As arquiteturas superescalares incluem todos os aspectos do pipeline e ainda acrescentam o fato de as instruções poderem estar executando no mesmo estágio do ''pipelining'' (em linhas pipelining diferentes). | |||

Cada processador possui acesso total ao cache, à memória RAM, e aos demais componentes do micro. | |||

Foi incluída também, uma unidade de controle, com a função de comandar o funcionamento dos dois processadores e dividir as tarefas entre eles. | |||

'''Observação:''' | |||

Teoricamente, o uso de dois processadores distintos dobraria o desempenho do Pentium, já que ao invés de uma, poderiam ser executadas duas instruções por ciclo de clock. Mas, na prática existem algumas limitações. | |||

Se por exemplo, um programa ordena que o processador some 4 números, X + Y + W + K, o processador poderia no primeiro ciclo de clock usar o pipeline U para somar X e Y e o pipeline V para somar W, mas no segundo ciclo, haveria apenas mais um cálculo para ser executado, o resultado das duas somas. | |||

Neste caso, apenas um dos pipelines poderia ser usado; o segundo ficaria ocioso. | |||

No final das contas, houve um ganho de 33%, já que ao invés do processador demorar 3 ciclos para executar o cálculo, demorou apenas 2. | |||

Assim, em média, a segunda canalização permite um desempenho 30 ou 40% superior ao desempenho obtido com apenas uma canalização. | |||

Caso o software seja alterado e otimizado para rodar em um processador com dois pipelines, ordenando as instruções de modo a deixar o segundo pipeline ocupado durante a maior parte do tempo, podemos conseguir mais 10 ou 15% de desempenho, chegando a algo entre 40 e 50%, mas, jamais será possível conseguir o dobro de desempenho. | |||

==Dependência de desvios== | |||

A presença de desvios condicionais em uma seqüência de instruções complica a operação do pipeline. | |||

A instrução seguinte a um desvio condicional (tomado ou não) depende dessa instrução de desvio. | |||

Esse tipo de dependência também afeta uma pipeline escalar, mas a conseqüência desse tipo de dependência é mais severa em uma pipeline superescalar, porque o número de instruções perdidas em cada atraso é maior. | |||

Se forem usadas instruções de tamanho variável, surge ainda um outro tipo de dependência. | |||

Como o tamanho de uma instrução particular não é conhecido, uma instrução deve ser decodificada, pelo menos parcialmente, antes que a instrução seguinte possa ser buscada. | |||

Isso impede a busca simultânea de instruções, requerida em uma pipeline superescalar. | |||

Essa é uma das razões pelas quais técnicas supersescalares são mais diretamente aplicáveis a arquiteturas RISC ou do tipo RISC, que possuem instruções de tamanho fixo. | |||

==Conflito de recursos== | |||

Um conflito de recurso ocorre quando duas ou mais instruções competem, ao mesmo tempo, por um mesmo recurso. | |||

Exemplos de recursos incluem memórias, caches, barramentos, portas de bancos de registradores e unidades funcionais (por exemplo, o somador da ULA). | |||

Em termos de pipeline, um conflito de recurso apresenta um comportamento semelhante ao de uma dependência de dados. | |||

Existem, entretanto, algumas diferenças. | |||

Por um lado, conflitos de recursos podem ser superados pela duplicação de recursos, enquanto uma dependência de dados não pode ser eliminada. | |||

dados | |||

Além disso, quando uma operação efetuada em uma dada unidade funcional consome muito tempo para ser completada, é possível minimizar os conflitos de uso dessa unidade por meio de sua implementação como uma pipeline. | |||

ser | |||

= | =Multiprocessadores simétricos= | ||

Até muito recentemente, quase todos os computadores pessoais e a maioria das estações de trabalho continham um único microprocessador de uso geral. | |||

Com a crescente demanda por desempenho e a contínua queda do custo dos microprocessadores, os fabricantes introduziram os sistemas SMP. | |||

A denominação SMP refere-se tanto à arquitetura de hardware do computador, quanto ao comportamento do sistema operacional sobre esta arquitetura. | |||

Um computador SMP pode ser definido como: | |||

# Existem dois ou mais processadores similares, com capacidade de processamento comparável; | |||

# Estes dois processadores compartilham a mesma memória principal e dispositivos de E/S, e são conectados por barramento interno, de forma que o tempo de acesso à memória em todos é praticamente o mesmo; | |||

# Todos os processadores compartilham acesso aos dispositivos de E/S; | |||

# Todos os processadores são capazes de desempenhar as mesmas funções; | |||

# Tudo é controlado por um sistema operacional integrado, que provê interação entre os processadores e seus programas, em nível de tarefas, de arquivos e de dados. | |||

O sistema operacional (SO) é quem efetua o escalonamento de processos ou fluxos de execução (ou ''threads''), sobre todos os processadores. | |||

Neste momento, é importante diferenciar entre as duas abordagens: os '''processadores paralelos''' e os '''sistemas paralelos'''. | |||

Como já foi visto, processadores paralelos, ou superescalares, exploram o paralelismo em '''nível de instruções''', isto é, de maneira a executar mais de uma instrução por ciclo de clock, em unidades diferentes de um mesmo processador. | |||

Já os sistemas paralelos, ou '''DISTRIBUÍDOS''' aonde se enquadram os computadores SMP, consistem basicamente da distribuição de tarefas entre vários processadores, ao mesmo tempo. | |||

Podem ser processadores ou computadores distintos, ou mesmo conjuntos de componentes interligados em rede que cooperam para realizar um conjunto de tarefas. | |||

==Vantagens== | |||

A arquitetura SMP tem uma série de vantagens sobre uma arquitetura uniprocessador: | |||

* Desempenho - se o trabalho efetuado pelo computador pode ser organizado de forma que algumas porções desse trabalho possam ser feitas em paralelo, então um sistema com múltiplos processadores resulta em maior desempenho que um sistema uniprocessador; | |||

* Disponibilidade - em um multiprocessador simétrico, como todos os processadores são similares e ativos, uma falha em um deles não ocasiona a parada de todo o sistema; | |||

* Crescimento incremental - o usuário pode aumentar o desempenho do sistema adicionando mais processadores; | |||

* Escalabilidade - fabricantes podem oferecer uma larga faixa de produtos, com características de desempenho e custo diferentes, com base no número de processadores configurados para o sistema. | |||

==Desvantagem== | |||

A principal desvantagem da arquitetura SMP é o da coerência de cache. Cada processador possui sua própria memória cache e é possível que uma determinada linha de dados esteja presente em mais de uma delas. | |||

Se esta linha for alterada, então, tanto a memória principal como todas as demais caches terão uma versão inválida desta linha. | |||

Estratégia: [https://pt.wikipedia.org/wiki/Protocolo_MESI protocolo MESI] | |||

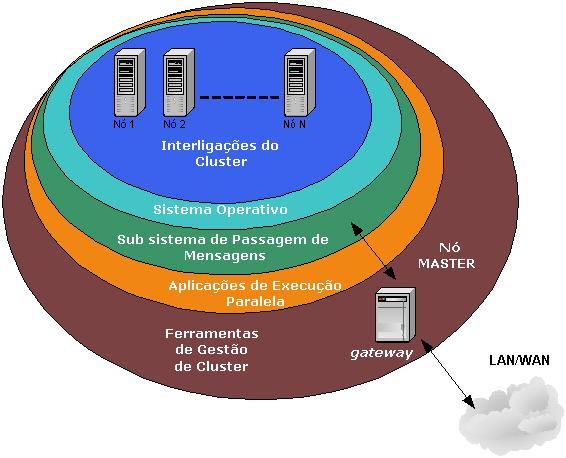

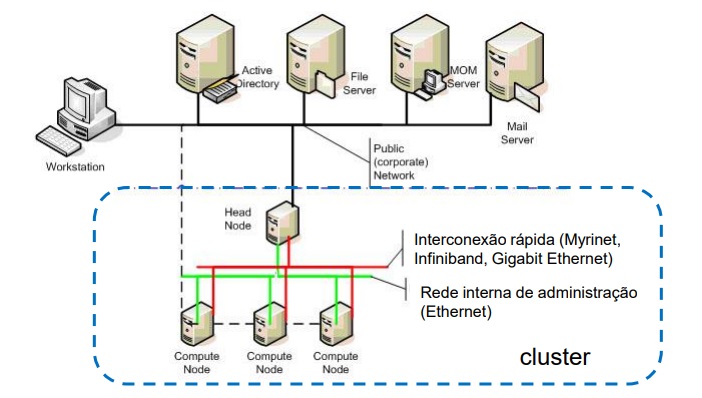

=Clusters= | |||

É uma das áreas mais promissoras de projeto de sistemas de computação da atualidade. | |||

[https://pt.wikipedia.org/wiki/Cluster '''''Clusters'''''] são agregados, ou aglomerados de computadores completos interconectados, trabalhando juntos, como um recurso de computação unificado que cria a ilusão de se constituir em uma única máquina. | |||

Cada computador completo do cluster é chamado de ''nó''. | |||

Estes nós de processamento (não necessariamente homogêneos) atuam de maneira que um processo de grande consumo seja executado no nó "mais disponível", ou mesmo subdividido por vários nós. | |||

[[image: MIPprocparal.png|center]] | |||

Cada nó tem sua própria memória local (não compartilhada) | |||

* Comunicação por troca de mensagens | |||

* Conceito cliente-servidor | |||

[https://www.opservices.com.br/o-que-e-um-cluster/ Tipos de Cluster] | |||

Outro link: [https://www.infowester.com/cluster.php] | |||

[[image: MIPcluster.png|center]] | |||

==Vantagens== | |||

* Escalabilidade | |||

* Alta disponibilidade | |||

* Melhor relação custo/desempenho | |||

==Desvantagens== | |||

* Difícil programação | |||

* Modelo de programação diferente | |||

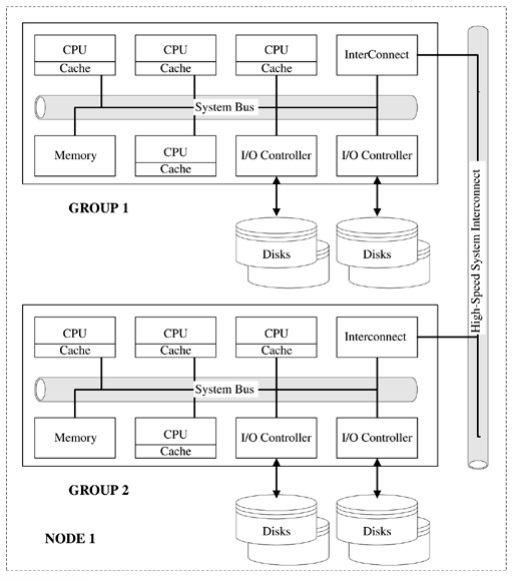

=Acesso não-Uniforme à Memória (NUMA)= | |||

= | NUMA = Non-Uniform Memory Acess | ||

Em um sistema SMP, existe um limite prático para o número de processadores que podem ser usados. A degradação de desempenho causada pelo gargalo dos barramentos parece limitar o número de processadores em uma configuração SMP a algum valor entre 16 e 64 processadores. | |||

Esta é a principal motivação do desenvolvimento de clusters, ao invés de sistemas SMP. | |||

Entretanto, em um cluster, cada nó tem sua própria memória principal privativa; as aplicações não ''enxergam'' uma grande memória global. | |||

De fato, a coerência de dados é mantida por software, não por hardware. | |||

Uma abordagem para obter um multiprocessamento em larga escala, mantendo o estilo SMP, é a abordagem NUMA (até 1024 processadores). | |||

O objetivo de um sistema NUMA é manter, de forma transparente, uma visão de grande e única área de memória no sistema, permitindo, ao mesmo tempo, vários nós multiprocessadores, cada qual com sue próprio barramento, ou outro sistema interno de interconexão. | |||

[[image: MIPparalel9.png|center]] | |||

O sistema NUMA consiste de um multiprocessador com memória compartilhada, no qual o tempo gasto por um certo processador para fazer acesso a uma palavra na memória varia de acordo com a posição desta palavra na memória. | |||

* Grupos de processadores com sua respectiva memória | |||

* Tempos de acesso à memória diferentes | |||

* Mantém modelo de memória compartilhada (mas precisa cuidados para obter desempenho) | |||

Cada nó do sistema NUMA inclui alguma memória principal. Entretanto, do ponto de vista dos processadores, existe uma única área de memória endereçável, com cada posição de memória tendo um endereço único em todo o sistema. | |||

Quando um processador inicia um acesso à memória, se a posição de memória requerida não está presente na cache L1, a cache L2 inicia uma operação de busca. | |||

Se a linha requerida está na porção LOCAL da MP, ela é obtida por meio do barramento local. | |||

Se a linha está em uma porção REMOTA da MP, então é automaticamente enviada uma requisição para buscar a linha por meio da rede de interconexão e entregue ao barramento local, que então a transfere para a cache requisitante. | |||

Toda esta atividade é feita de forma automática e transparente para o processador e para sua cache. | |||

Edição atual tal como às 15h52min de 26 de junho de 2018

Por que estudar paralelismo?

- Explora alternativas de projeto de novos sistemas para aumento de desempenho e de recursos de microeletrônica.

- Área de pesquisa com uma comunidade brasileira ativa e atuante em várias áreas e forte apelo internacional

- Áreas de atuação:

- Desenvolvimento de novos modelos de computação

- Desenvolvimento de novas arquiteturas de sistemas computacionais (processadores multi-core, multiprocessadores, sistemas de cluster, grid e cloud computing)

- Viabiliza novas aplicações computacionais (modelos matemáticos):

– Previsão de tempo e de clima

– Drug design, genômica, proteômica

– Simulação (car crash, plataforma petrolífera, ...)

Paralelismo e processamento superescalar

Além de tudo que foi visto, em termos de aprimoramento dos módulos internos do processador, barramentos, memórias, etc, inúmeras outras estratégias foram criadas com o intuito de aumentar a velocidade dos sistemas computacionais.

Em uma das linhas de pesquisa, ao invés de se pensar em um único processador com características superiores, os desenvolvedores começaram a seguir a abordagem de utilizar vários sub-sistemas de processamento acoplados, ou seja, por meio da estratégia "dividir para conquistar".

Tipos de sistemas com processadores paralelos

Taxonomia proposta por Flymm (1972):

Única instrução, único dado (SISD - single instruction, single data)

Um único processador executa uma única sequência de instruções, usando dados armazenados em uma única memória.

Exemplo: Máquina de Von Neumann

Única instrução, múltiplos dados (SIMSD - single instruction, multiple data)

Nestes computadores, ocorre a execução síncrona da instrução, para todos os dados.

Uma única instrução de máquina controla a execução simultânea de um certo número de elementos de processamento, em passos de execução.

Cada elemento de processamento tem uma memória de dados a ele associada, de modo que cada instrução é executada sobre um conjunto de dados diferente em cada processador.

Os processadores vetoriais e matriciais pertencem a essa categoria.

Exemplos:

- Processadores vetoriais (Cray 1)

- GPU - ou graphics processing unit, Unidade Gráfica de Processamento

Múltiplas instruções, único dado (MISD - multiple instruction, single data)

Uma sequência de dados é transmitida para um conjunto de processadores, cada um dos quais executa uma sequência de instruções diferente.

Isto é, várias instruções são executadas em um único fluxo de dados.

Essa estrutura nunca foi implementada.

Múltiplas instruções, múltiplos dados (MIMD - multiple instruction, multiple data)

Permite a execução de instruções diferentes para cada um dos dados.

Ou seja, um conjunto de processadores executa simultaneamente sequências diferentes de instruções, sobre conjuntos de dados distintos.

Os SMPs, clusters e sistemas NUMA pertencem a esta categoria.

Exemplos:

- Arquiteturas paralelas atuais

- Top500.org

Em uma organização MIMD, os processadores são de propósito geral; cada um pode processar todas as instruções necessárias para realizar a transformação de dados apropriada.

Outras classificações para Paralelismo

Há várias fontes de execução paralela em um computador moderno.

Paralelismo no Nível de Instrução (ILP)

Permite executar várias instruções em cada ciclo de relógio.

Modificações na microarquitetura do processador para possibilitar a execução paralela de instruções.

Abordagens:

- Paralelismo temporal: encadeamento no fluxo de execução das instruções (pipeline);

- Paralelismo na emissão de instruções: submissão de várias instruções para execução pelo fluxo de dados (VLIW - very long instruction line (128 bits) e superescalaridade);

- Paralelismo de dados: permite executar várias instâncias da mesma instrução para um conjunto de dados (processamento SIMD ou vetorial).

Pipelining

Arquiteturas de processador Superescalares

Processadores Superescalares são todos os que possuem mais de uma unidade funcional em cada pipeline, as quais permitem a execução de mais de uma instrução simultaneamente (no mesmo ciclo de clock).

A arquitetura pipeline já permite que diversas instruções sejam executadas ao mesmo tempo, desde que estejam em estágios diferentes do pipeline.

Porém, ainda que várias instruções sejam executadas concorrentemente (em cada estágio do pipeline), apenas uma instrução encontra-se na fase de execução, ou seja, o sistema continua sendo SISD.

Já na arquitetura superescalar, várias instruções podem ser iniciadas simultaneamente e executadas independentemente umas das outras.

A partir do Pentium, a maioria dos processadores para computadores pessoais atualmente são superescalares.

Isto é obtido através da implementação de múltiplas unidades funcionais, que são unidades onde as instruções são executadas.

O Pentium, por exemplo, trabalha internamente como se fosse composto por dois processadores de 32 bits distintos (chamados de pipeline U e pipeline V), sendo capaz de processar duas instruções por ciclo de clock (uma em cada pipeline).

As arquiteturas superescalares incluem todos os aspectos do pipeline e ainda acrescentam o fato de as instruções poderem estar executando no mesmo estágio do pipelining (em linhas pipelining diferentes).

Cada processador possui acesso total ao cache, à memória RAM, e aos demais componentes do micro.

Foi incluída também, uma unidade de controle, com a função de comandar o funcionamento dos dois processadores e dividir as tarefas entre eles.

Observação:

Teoricamente, o uso de dois processadores distintos dobraria o desempenho do Pentium, já que ao invés de uma, poderiam ser executadas duas instruções por ciclo de clock. Mas, na prática existem algumas limitações. Se por exemplo, um programa ordena que o processador some 4 números, X + Y + W + K, o processador poderia no primeiro ciclo de clock usar o pipeline U para somar X e Y e o pipeline V para somar W, mas no segundo ciclo, haveria apenas mais um cálculo para ser executado, o resultado das duas somas. Neste caso, apenas um dos pipelines poderia ser usado; o segundo ficaria ocioso. No final das contas, houve um ganho de 33%, já que ao invés do processador demorar 3 ciclos para executar o cálculo, demorou apenas 2.

Assim, em média, a segunda canalização permite um desempenho 30 ou 40% superior ao desempenho obtido com apenas uma canalização.

Caso o software seja alterado e otimizado para rodar em um processador com dois pipelines, ordenando as instruções de modo a deixar o segundo pipeline ocupado durante a maior parte do tempo, podemos conseguir mais 10 ou 15% de desempenho, chegando a algo entre 40 e 50%, mas, jamais será possível conseguir o dobro de desempenho.

Dependência de desvios

A presença de desvios condicionais em uma seqüência de instruções complica a operação do pipeline.

A instrução seguinte a um desvio condicional (tomado ou não) depende dessa instrução de desvio.

Esse tipo de dependência também afeta uma pipeline escalar, mas a conseqüência desse tipo de dependência é mais severa em uma pipeline superescalar, porque o número de instruções perdidas em cada atraso é maior.

Se forem usadas instruções de tamanho variável, surge ainda um outro tipo de dependência.

Como o tamanho de uma instrução particular não é conhecido, uma instrução deve ser decodificada, pelo menos parcialmente, antes que a instrução seguinte possa ser buscada.

Isso impede a busca simultânea de instruções, requerida em uma pipeline superescalar.

Essa é uma das razões pelas quais técnicas supersescalares são mais diretamente aplicáveis a arquiteturas RISC ou do tipo RISC, que possuem instruções de tamanho fixo.

Conflito de recursos

Um conflito de recurso ocorre quando duas ou mais instruções competem, ao mesmo tempo, por um mesmo recurso.

Exemplos de recursos incluem memórias, caches, barramentos, portas de bancos de registradores e unidades funcionais (por exemplo, o somador da ULA).

Em termos de pipeline, um conflito de recurso apresenta um comportamento semelhante ao de uma dependência de dados.

Existem, entretanto, algumas diferenças.

Por um lado, conflitos de recursos podem ser superados pela duplicação de recursos, enquanto uma dependência de dados não pode ser eliminada.

Além disso, quando uma operação efetuada em uma dada unidade funcional consome muito tempo para ser completada, é possível minimizar os conflitos de uso dessa unidade por meio de sua implementação como uma pipeline.

Multiprocessadores simétricos

Até muito recentemente, quase todos os computadores pessoais e a maioria das estações de trabalho continham um único microprocessador de uso geral.

Com a crescente demanda por desempenho e a contínua queda do custo dos microprocessadores, os fabricantes introduziram os sistemas SMP.

A denominação SMP refere-se tanto à arquitetura de hardware do computador, quanto ao comportamento do sistema operacional sobre esta arquitetura.

Um computador SMP pode ser definido como:

- Existem dois ou mais processadores similares, com capacidade de processamento comparável;

- Estes dois processadores compartilham a mesma memória principal e dispositivos de E/S, e são conectados por barramento interno, de forma que o tempo de acesso à memória em todos é praticamente o mesmo;

- Todos os processadores compartilham acesso aos dispositivos de E/S;

- Todos os processadores são capazes de desempenhar as mesmas funções;

- Tudo é controlado por um sistema operacional integrado, que provê interação entre os processadores e seus programas, em nível de tarefas, de arquivos e de dados.

O sistema operacional (SO) é quem efetua o escalonamento de processos ou fluxos de execução (ou threads), sobre todos os processadores.

Neste momento, é importante diferenciar entre as duas abordagens: os processadores paralelos e os sistemas paralelos.

Como já foi visto, processadores paralelos, ou superescalares, exploram o paralelismo em nível de instruções, isto é, de maneira a executar mais de uma instrução por ciclo de clock, em unidades diferentes de um mesmo processador.

Já os sistemas paralelos, ou DISTRIBUÍDOS aonde se enquadram os computadores SMP, consistem basicamente da distribuição de tarefas entre vários processadores, ao mesmo tempo.

Podem ser processadores ou computadores distintos, ou mesmo conjuntos de componentes interligados em rede que cooperam para realizar um conjunto de tarefas.

Vantagens

A arquitetura SMP tem uma série de vantagens sobre uma arquitetura uniprocessador:

- Desempenho - se o trabalho efetuado pelo computador pode ser organizado de forma que algumas porções desse trabalho possam ser feitas em paralelo, então um sistema com múltiplos processadores resulta em maior desempenho que um sistema uniprocessador;

- Disponibilidade - em um multiprocessador simétrico, como todos os processadores são similares e ativos, uma falha em um deles não ocasiona a parada de todo o sistema;

- Crescimento incremental - o usuário pode aumentar o desempenho do sistema adicionando mais processadores;

- Escalabilidade - fabricantes podem oferecer uma larga faixa de produtos, com características de desempenho e custo diferentes, com base no número de processadores configurados para o sistema.

Desvantagem

A principal desvantagem da arquitetura SMP é o da coerência de cache. Cada processador possui sua própria memória cache e é possível que uma determinada linha de dados esteja presente em mais de uma delas.

Se esta linha for alterada, então, tanto a memória principal como todas as demais caches terão uma versão inválida desta linha.

Estratégia: protocolo MESI

Clusters

É uma das áreas mais promissoras de projeto de sistemas de computação da atualidade.

Clusters são agregados, ou aglomerados de computadores completos interconectados, trabalhando juntos, como um recurso de computação unificado que cria a ilusão de se constituir em uma única máquina.

Cada computador completo do cluster é chamado de nó.

Estes nós de processamento (não necessariamente homogêneos) atuam de maneira que um processo de grande consumo seja executado no nó "mais disponível", ou mesmo subdividido por vários nós.

Cada nó tem sua própria memória local (não compartilhada)

- Comunicação por troca de mensagens

- Conceito cliente-servidor

Outro link: [1]

Vantagens

- Escalabilidade

- Alta disponibilidade

- Melhor relação custo/desempenho

Desvantagens

- Difícil programação

- Modelo de programação diferente

Acesso não-Uniforme à Memória (NUMA)

NUMA = Non-Uniform Memory Acess

Em um sistema SMP, existe um limite prático para o número de processadores que podem ser usados. A degradação de desempenho causada pelo gargalo dos barramentos parece limitar o número de processadores em uma configuração SMP a algum valor entre 16 e 64 processadores.

Esta é a principal motivação do desenvolvimento de clusters, ao invés de sistemas SMP.

Entretanto, em um cluster, cada nó tem sua própria memória principal privativa; as aplicações não enxergam uma grande memória global.

De fato, a coerência de dados é mantida por software, não por hardware.

Uma abordagem para obter um multiprocessamento em larga escala, mantendo o estilo SMP, é a abordagem NUMA (até 1024 processadores).

O objetivo de um sistema NUMA é manter, de forma transparente, uma visão de grande e única área de memória no sistema, permitindo, ao mesmo tempo, vários nós multiprocessadores, cada qual com sue próprio barramento, ou outro sistema interno de interconexão.

O sistema NUMA consiste de um multiprocessador com memória compartilhada, no qual o tempo gasto por um certo processador para fazer acesso a uma palavra na memória varia de acordo com a posição desta palavra na memória.

- Grupos de processadores com sua respectiva memória

- Tempos de acesso à memória diferentes

- Mantém modelo de memória compartilhada (mas precisa cuidados para obter desempenho)

Cada nó do sistema NUMA inclui alguma memória principal. Entretanto, do ponto de vista dos processadores, existe uma única área de memória endereçável, com cada posição de memória tendo um endereço único em todo o sistema.

Quando um processador inicia um acesso à memória, se a posição de memória requerida não está presente na cache L1, a cache L2 inicia uma operação de busca.

Se a linha requerida está na porção LOCAL da MP, ela é obtida por meio do barramento local.

Se a linha está em uma porção REMOTA da MP, então é automaticamente enviada uma requisição para buscar a linha por meio da rede de interconexão e entregue ao barramento local, que então a transfere para a cache requisitante.

Toda esta atividade é feita de forma automática e transparente para o processador e para sua cache.