AULA 9 - Microprocessadores - Graduação: mudanças entre as edições

imported>Fargoud |

imported>Fargoud |

||

| Linha 140: | Linha 140: | ||

** '''Programa (Software)''': gerada por alguma condição que ocorra como resultado da execução de uma instrução. Ex: overflow, divisão por zero, instrução ilegal etc. | ** '''Programa (Software)''': gerada por alguma condição que ocorra como resultado da execução de uma instrução. Ex: overflow, divisão por zero, instrução ilegal etc. | ||

** '''''Timer''''': gerada pelo processamento interno do relógio (timer). Usado em sistemas sistemas multi-tarefa preemptivos para executar certas funções a intervalos regulares de tempo. | ** '''''Timer''''': gerada pelo processamento interno do relógio (timer). Usado em sistemas sistemas multi-tarefa preemptivos para executar certas funções a intervalos regulares de tempo. | ||

** ''E/S'': gerada pelo módulo de E/S para sinalizar a conclusão uma operação ou a ocorrência de uma situação de erro. | ** '''E/S''': gerada pelo módulo de E/S para sinalizar a conclusão uma operação ou a ocorrência de uma situação de erro. | ||

** ''Falha de Hardware'': gerada na ocorrência de uma falha. Ex: queda de energia, erro de paridade de memória | ** '''Falha de Hardware''': gerada na ocorrência de uma falha. Ex: queda de energia, erro de paridade de memória | ||

===Controle do fluxo do programa=== | ===Controle do fluxo do programa=== | ||

Edição das 13h49min de 30 de abril de 2019

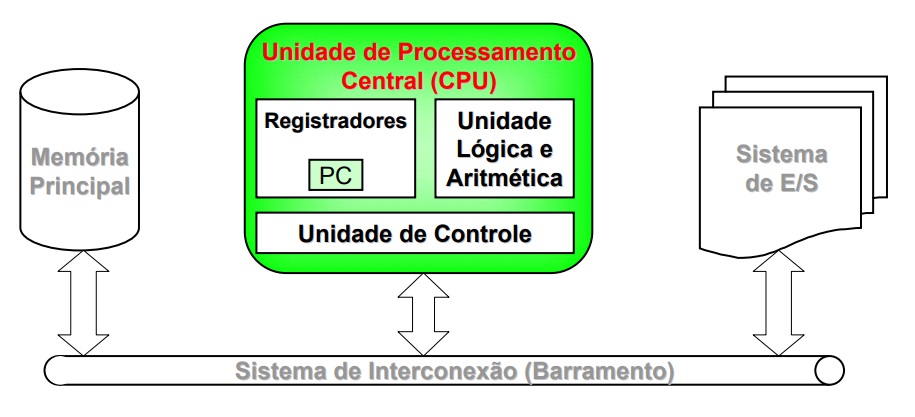

CPU - Unidade de Controle

A CPU é o "cérebro" do processador.

- Funções:

- Interpretação e execução dos programas da memória principal;

- Controle dos demais componentes.

Componentes

- Registradores - armazenam armazenam temporariamente dados e instruções.

- Unidade Lógica e Aritmética (ULA)- “processa” os dados e atualiza os registradores.

- Unidade de Controle (UC) - “dispara” cada um das etapas de execução da instrução.

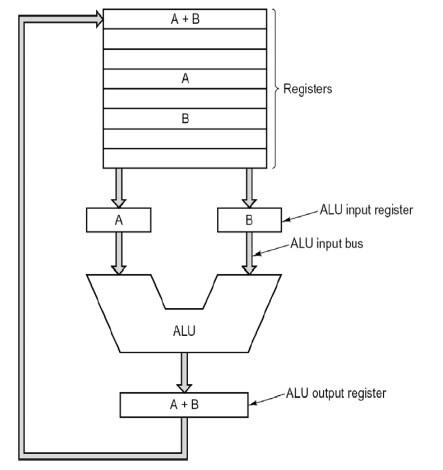

ULA

é o “núcleo” da CPU.

- Executa as operações de processamento de dados. Podem ser diferentes para cálculos com inteiros e ponto flutuante.

- Ativa bits especiais (flags), como resultado da operação. Ex: operação nula (bit Z), operação negativa (bit N), overflow, etc.

- Está conectada a um grupo de registradores pelo barramento interno, formando o caminho de dados.

- Pode-se utilizar um conjunto de conjunto de ULAs para a execução paralela de instruções.

Banco de registradores

Pequenas unidades de memória com alta velocidade.

- Mais rápidas que as memórias principal e cache.

- Utilizam o barramento interno da CPU.

Armazenamento temporário de dados, instruções e endereços, em utilização pelo processador.

- Possuem diferentes funções, mas têm um uso bem definido, dentro da arquitetura.

- Possibilitam operações de leitura e escrita.

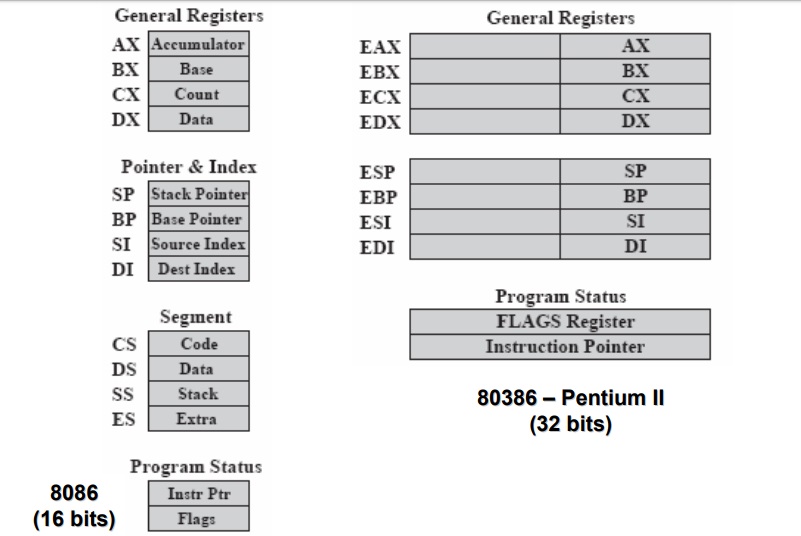

Registradores de uso geral

- Utilizados para armazenar dados que serão processados ou produzidos pela ULA. Ex: AX-DX, AC, R0-R13.

- Coletivamente são chamados conjunto de registradores de dados (data register file).

Registradores de controle

- Utilizados no controle das operações pela CPU e nas trocas de informações com a MP. Ex: PC, IR, MAR, MBR.

- Alguns desses são invisíveis aos programadores.

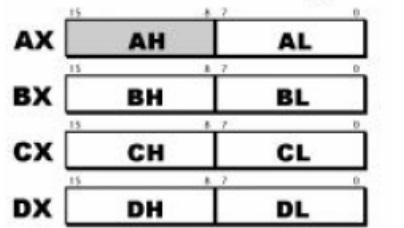

Registradores (Processador 8088/8086)

- CPU possui 14 registradores de 16 bits visíveis.

- 4 registradores de uso geral:

- AX (Acumulador): armazena operandos e resultados dos cálculos aritméticos e lógicos.

- BX (Base): armazena endereços indiretos.

- CX (Contador): conta iterações de loops ou especifica o n° de caracteres de uma string.

- DX (Dados): armazena overflow e endereço de E/S.

- Podem ser usados como registradores de 8 bits: Ex: AH e AL (byte alto e byte baixo de AX).

- 4 registradores de segmento:

- CS (Segmento de Código): contém o endereço da área com as instruções de máquina em execução.

- DS (Segmento de Dados): contém o endereço da área com os dados do programa. Geralmente aponta para as variáveis globais do programa.

- SS (Segmento de Pilha): contém o endereço da área com a pilha. Que armazena informações importantes sobre o estado da máquina, variáveis locais, endereços de retorno e parâmetros de subrotinas.

- ES (Segmento Extra): utilizado para ganhar acesso a alguma área da memória quando não é possível usar os outros registradores de segmento. Ex: transferências de bloco de dados.

- 5 registradores de offset:

- PC (Program Counter) ou IP (Instruction Pointer): usado em conjunto com o CS para apontar a próxima instrução.

- SI (source index) e DI (destiny index): utilizados para mover blocos de bytes de um lugar (SI) para outro (DI) e como ponteiros para endereçamento (junto com os registradores CS, DS, SS e ES).

- BP (Base Pointer): usado em conjunto com o SS para apontar a base da pilha. Similar ao registrador BX. Usado para acessar parâmetros e variáveis locais.

- SP (Stack Pointer): usado em conjunto com o SS para apontar o topo da pilha.

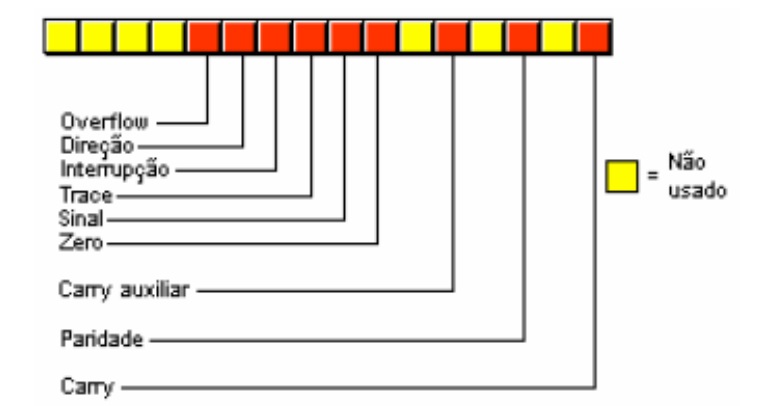

- 1 registrador de estado do processador (PSW) :

- Registrador especial composto por sinalizadores (flags) que ajudam a determinar o estado atual do processador. Coleção de valores de 1 bit. Apenas 9 bits são utilizados:

- 4 mais utilizados: ZF - zero; CF - carry ("vai um“) ou borrow (“vem um”); SF - sinal; e OF - overflow ou underflow.

Organização dos Registradores – Família Intel

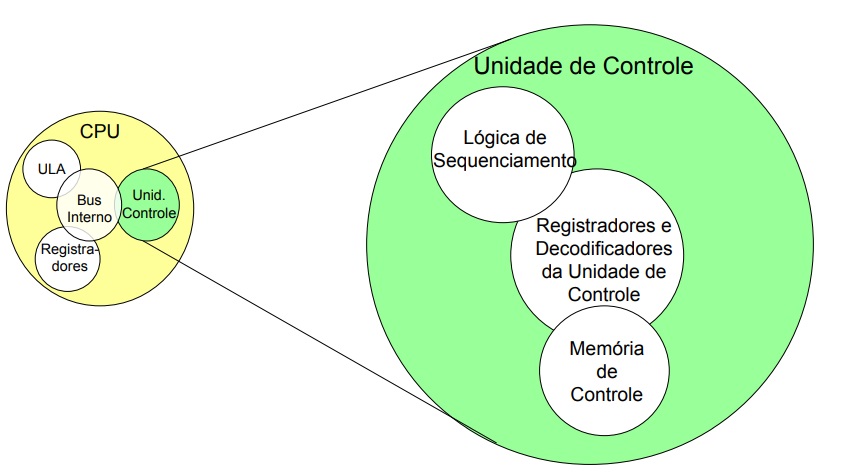

Unidade de Controle

- Gerencia os recursos disponíveis e o fluxo de dados entre os componentes.

- Controla a execução das instruções pela CPU:

- Busca as instruções na memória principal.

- Decodificação das instruções (geração dos sinais de controle correspondentes).

- Seqüenciamento das operações.

- Disparo da execução (envio dos sinais de controle).

- Representa uma das partes mais difíceis de ser projetada em um computador, devido à complexidade dos processadores.

Estrutura

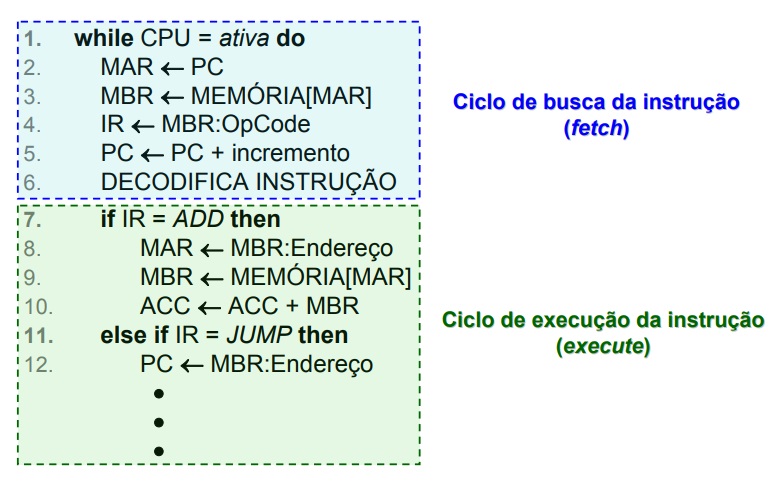

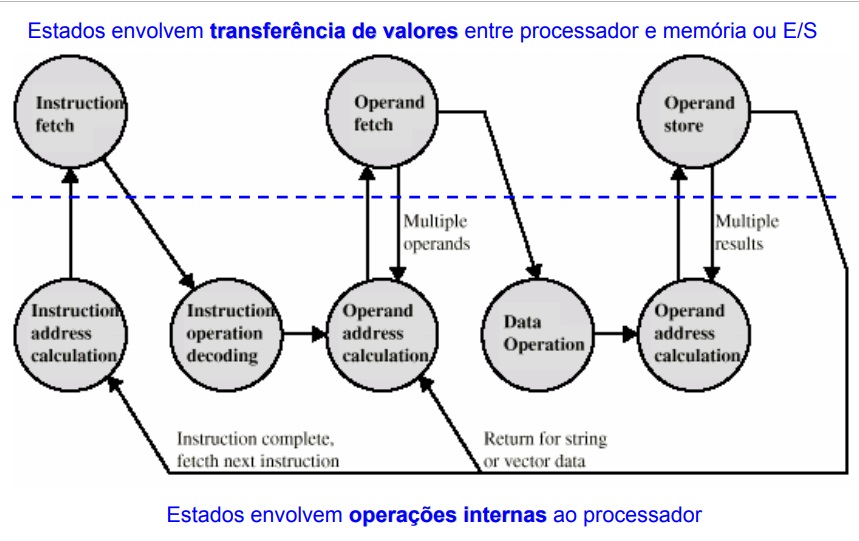

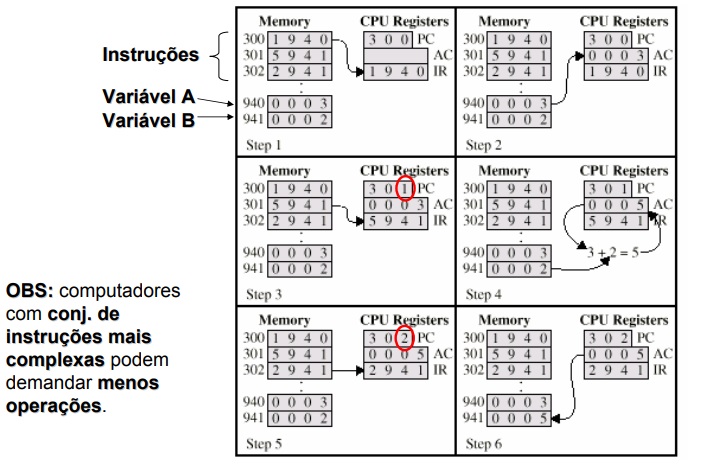

Ciclo de Ciclo de Busca-Execução (fetch-execute execute)

- Busca a instrução (memória → IR);

- Altera PC para indicar a próxima instrução;

- Decodifica a instrução atual;

- Determina o endereço e busca o operando na memória (quando necessário);

- Executa a operação (sinais de controle);

- Armazena os resultados;

- Repete passos anteriores.

Categorias de Instruções

- Movimentação processador – memória: Transferência de dados entre CPU e memória principal.

- Movimentação processador - E/S: Transferência de dados entre CPU e módulos de E/S.

- Processamento de dados: Realiza alguma operação lógica ou aritmética nos dados.

- Operações de controle: Alteração na seqüência de execução de instruções. Ex: desvios condicionais e não-condicionais (jump)

- Qualquer combinação das operações acima

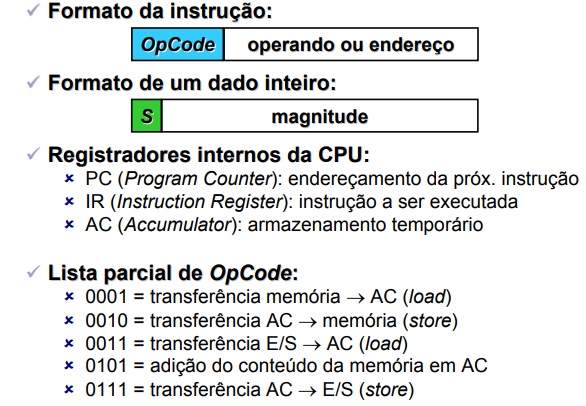

Máquina Hipotética (32 bits)

Interrupções

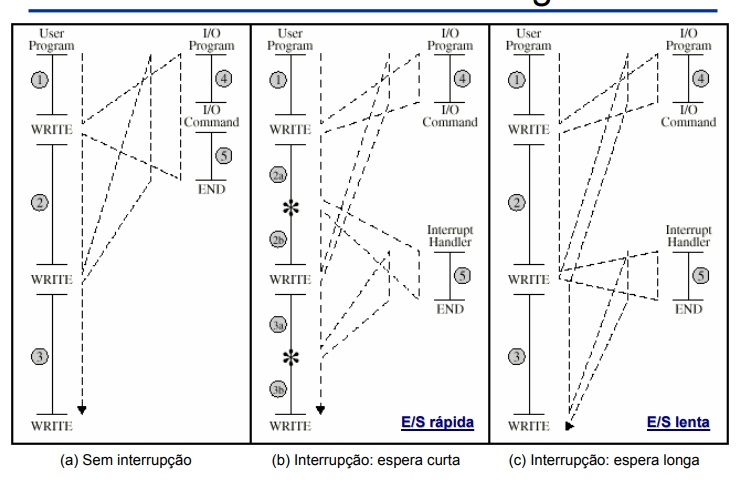

Mecanismos pelos quais outros componentes podem interromper a seqüência normal do processamento.

- Visa melhorar a eficiência do processamento.

- Fontes de interrupções mais comuns:

- Programa (Software): gerada por alguma condição que ocorra como resultado da execução de uma instrução. Ex: overflow, divisão por zero, instrução ilegal etc.

- Timer: gerada pelo processamento interno do relógio (timer). Usado em sistemas sistemas multi-tarefa preemptivos para executar certas funções a intervalos regulares de tempo.

- E/S: gerada pelo módulo de E/S para sinalizar a conclusão uma operação ou a ocorrência de uma situação de erro.

- Falha de Hardware: gerada na ocorrência de uma falha. Ex: queda de energia, erro de paridade de memória

Controle do fluxo do programa

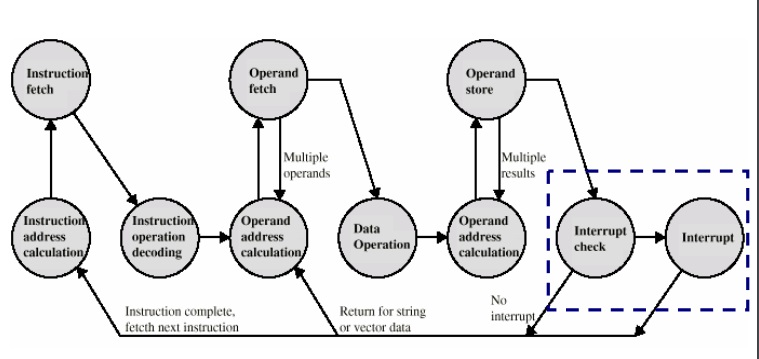

Ciclo de interrupção:

- Acrescentado ao ciclo de instrução.

- Processador verifica se há interrupção: Indicado por um sinal de interrupção.

- Se não há interrupção, busca a próxima instrução na memória.

- Se houver interrupção pendente:

- Suspende a execução do programa corrente.

- Salva o contexto na pilha.

- Configura PC com o endereço de início da rotina de rotina de tratamento da interrupção (interrupt handler routine).

- Processa a interrupção.

- Restaura o contexto.

- Continua a execução do programa interrompido.

Ciclo de Instruções com Interrupção

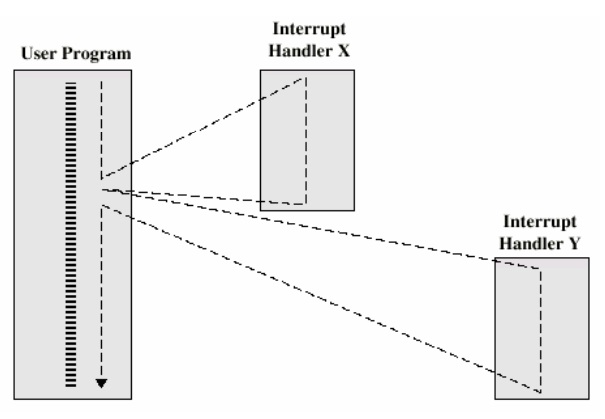

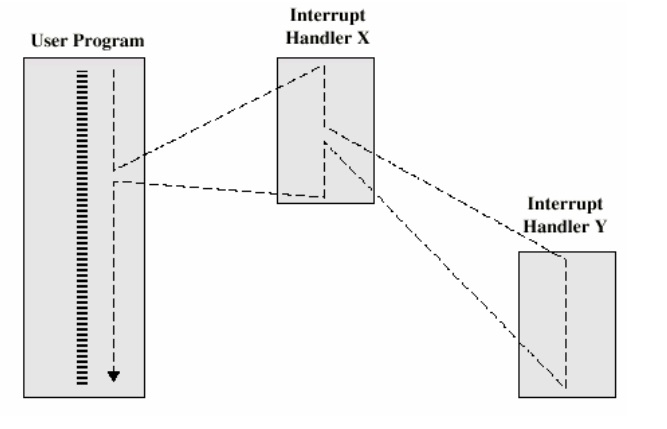

Múltiplas interrupções

Desabilitar interrup Desabilitar interrupções: 9 O processador ignora futuras interrup ignora futuras interrupções enquanto processa uma interrupção. 9 Interrupção são manipuladas na seq manipuladas na seqüência que elas acontecem. Definir prioridades Definir prioridades: 9 Interrupções de baixa prioridade são interrompidas por interrupções de alta prioridade. 9 Quando a interrupção de mais alta prioridade foi processada, o processador retorna a interrupção anterior.

Execução sequencial:

Execução aninhada:

Sinal de clock

Utilizado para atender as rela atender as relações de tempo requeridas ões de tempo requeridas nas operações (sincronismo sincronismo). Novas operações básicas são iniciadas em um novo ciclo novo ciclo de clock. A execução de uma instrução consome um certo nº de ciclos de clock. 9 Varia de acordo com o nº de opera de operações básicas requeridas sicas requeridas e o tempo de execu tempo de execução de cada ão de cada uma delas. O tamanho do ciclo de clock é um dos fatores que determinam o desempenho de um processador desempenho de um processador. 9 < tamanho do ciclo ⇒ < tempo de execução ⇒ > nº de instruções/seg.