AULA 7 - Microprocessadores - Graduação

Estrutura e Funcionamento da CPU

Neste capítulo estudaremos características da maioria das CPUs.

Pilhas

Uma pilha , ou stack é uma estrutura de dados ordenada do tipo LIFO (last-in-first-out), na qual apenas um dos elementos pode ser acessado, em um dado instante - o elemento do topo da pilha.

O tamanho da pilha, ou o número de elementos empilhados, é variável. Normalmente, existe um tamanho máximo de "níveis" da pilha, mas estes podem ser continuamente acrescentados ou removidos.

Quase todas as pilhas são controladas por 3 apontadores/ponteiros (variáveis que armazenam endereços de memória):

- o apontador que endereça o topo da pilha, normalmente chamado de TOP - este valor é incrementado ou decrementado, conforme a pilha aumenta ou diminui (até o limite máximo de LENGHT, e o limite mínimo de BOTTOM);

- o apontador que endereça o limite máximo de tamanho da pilha, muitas vezes chamado de LENGHT, e

- o apontador que endereça a base da pilha, também chamado de BOTTOM.

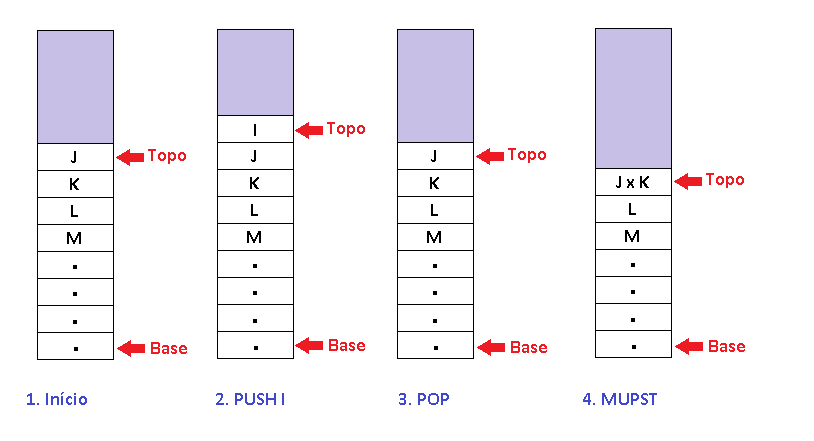

Normalmente, a instrução que empilha, isto é, coloca um novo dado no topo da pilha é a instrução PUSH. Da mesma forma, a instrução que desempilha, ou seja, remove o item do topo da pilha, normalmente, chama-se POP.

Na grande maioria dos casos, as pilhas são usadas nas CPUs para gerenciar a chamada e retorno de procedimento. Ou seja, é comum que se armazene endereço de retorno nas pilhas, ou status de registradores, etc.

Alguns processadores possuem pilhas para uso interno. Porém estas não estão disponíveis para os programadores.

Quando estiverem, instruções específicas para processamento nas pilhas, além de PUSH e POP, são desejáveis.

Por exemplo:

Note que a última instrução, MUPST, de MUltiPlica STack atuará sobre os dois últimos valores do topo da pilha.

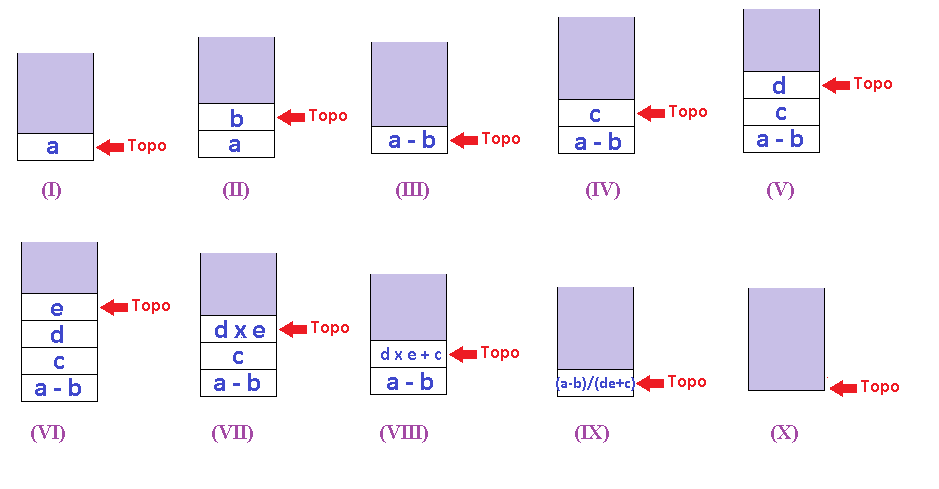

Na imensa maioria dos casos, as operações lógico-aritméticas nas pilhas seguem esta notação pós-fixa, também chamada de notação polonesa reversa. Nesta notação, o operador vem depois dos operandos.

Exemplo:

a + b ⇒ a b + a + (b x c) ⇒ a b c x + (a + b )x c ⇒ a b + c x

A figura abaixo ilustra todos os passos, e comportamento da pilha, se esta estivesse executando a sequência de instruções de pilha abaixo, para efetuar a operação f = (a - b)/(c + d x e):

(I) PUSH A (II) PUSH B (III) SUB (IV) PUSH C (V) PUSH D (VI) PUSH E (VII) MUL (VIII) ADD (IX) DIV (X) POP F

Representações Little-Endian, Big-Endian e Bi-Endian

A partir do momento em que os valores utilizados nas CPUs começaram a ultrapassar o limite de um byte (8 bits), surgiu a dúvida: "como dispor estes bytes componentes de cada palavra na memória?"

Byte menos significativos em endereços mais baixos da memória, ou vice-versa.

Por exemplo:

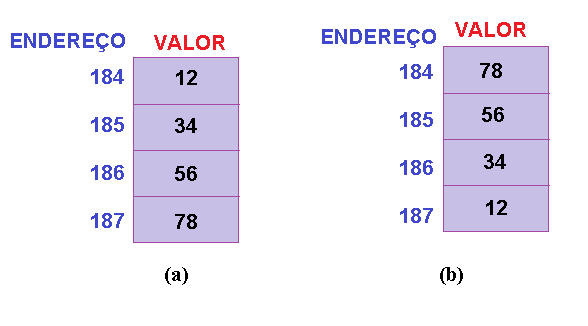

Seja o valor hexadecimal 12345678h, armazenado em 32 bits, a partir da posição de memória 184, em memória endereçável a cada byte.

No mapeamento mostrado à esquerda, em (a), o byte mais significativo é armazenado no menor endereço de byte. Isto é conhecido como representação big-endian e é equivalente à ordem de escrita ocidental.

No mapeamento mostrado à direita, em (b), o byte menos significativo é armazenado no menor endereço de byte. Isto é conhecido como representação little-endian, e é remanescente da ordem de avaliação das operações aritméticas, da direita para a esquerda.

Modos de Endereçamento

Máquinas CISC x RISC

Paradigma CISC •Complex Instruction Set Computer –Conjunto de instruções inicialmente simples –Avanços tecnológicos permitiram a fabricação de computadores com mais transistores e menor custo –Projetistas optaram por conjuntos de instruções cada vez mais complexos •Intenção: reduzir a distância semântica entre Assembly e linguagens de alto nível

Instruções com elevado grau semântico •Elevado número de modos de endereçamento (ex: endereçamento indireto em memória) •Elevado número de ciclos de clock por instrução → redução da frequência de clock •Menor número de instruções por programa → menor uso de memória de código •Decodificação através de microcódigo → dificulta/impossibilita o uso de pipeline

Reduced Instruction Set Computer –Instruções simples que executam rápido –Elevado número de registradores de uso geral –Decodificação de instruções com lógica combinacional (tabela) –Execução utilizando pipeline → um ciclo de clock por instrução

Paradigma RISC •Regularidade de tempo de execução •Regularidade de tamanho de instrução •Redução da área de silício e tempo de projeto •Efeito final: melhor desempenho, apesar do número de instruções por programa ser maior