AULA 15 - Microprocessadores - Graduação

Paralelismo e processamento superescalar

Além de tudo que foi visto, em termos de aprimoramentos de arquiteturas de processador, barramentos, memórias, etc, inúmeras outras estratégias foram criadas com o intuito de aumentar a velocidade dos sistemas computacionais.

Em uma das linhas de pesquisa, ao invés de se pensar em um único processador com características superiores, os desenvolvedores começaram a seguir a abordagem de utilizar vários sub-sistemas de processamento acoplados, ou seja, por meio da estratégia "dividir para conquistar".

Basicamente existem duas abordagens: os processadores paralelos e os sistemas paralelos.

Processadores paralelos, ou superescalares exploram paralelismo em nível de instruções, de maneira a capacitar a execução de mais de uma instrução por ciclo de clock.

Este tipo de processador decodifica múltiplas instruções de uma vez e o resultado de instruções de desvio condicional são geralmente preditas antecipadamente, durante a fase de busca, para assegurar um fluxo ininterrupto.

Arquiteturas Superescalares

Assim, como arquiteturas “Pipelined”, com Desempenho Superior ao de uma Instrução por Ciclo foram propostas as seguintes metodologias:

- Arquiteturas Superescalares - Execução de múltiplas instruções, escalonadas por hardware e/ou software, concorrentemente.

- Arquiteturas VLIW (Very Long Instruction Word) - Execução de múltiplas operações, escalonadas por “software”, concorrentemente.

- Arquiteturas Multithreading e SMT - Executam instruções de mais de um fluxo (threads) simultaneamente.

- Arquiteturas Multicore - Combinação de vários processadores de um mesmo tipo (acima descrito) em uma única pastilha.

Arquiteturas Superescalares

Organizadas internamente como múltiplos “pipelines”

e com banco de registradores com múltiplas portas de

leitura e de escrita, com múltiplas instruções iniciadas

e terminadas a cada ciclo. O grau de concorrência das

instruções situa-se na prática entre 2 e 4.

As instruções são despachadas para execução

somente quando não violam regras de dependência de

dados, de controle e quando não existem conflitos

estruturais.

• O escalonamento das instruções pode ser feito por

“software” e/ou por “hardware”.

• O código objeto para estas arquiteturas é compatível

com o de arquiteturas escalares convencionais.

Arquiteturas Superescalares

Capacidade para realizar busca e decodificação

de múltiplas instruções por ciclo;

Existência de uma Janela de Instruções que isola

os estágios de busca e decodificação dos estágios

de execução propriamente dita da instrução

modelo de despacho fora-de-ordem:

Janela Centralizada

Estações de Reserva (Algoritmo de

Tomasulo)

Esquemas eficientes de predição dinâmica de

desvios;

Arquiteturas Superescalares

Recuperação do estado da máquina em caso de

exceções ou de previsões erradas de desvios

Reorder Buffer;

Remoção de dependências de dados

Scoreboarding, Tomasulo e/ou Renomeação

Dinâmica;

Lógica de despacho concorrente para as

instruções armazenadas na Janela de I

Arquiteturas Superescalares

Múltiplos barramentos para comunicação de

operandos e resultados e Banco de Registradores com

múltiplas portas de leitura e de escrita, incluindo a

existência de lógica de arbitração se o número de

recursos é menor que o máximo possivelmente

necessário;

Múltiplas unidades funcionais: ALU, Ponto Flutuante,

Desvio, Load/Store;

Suporte para tratamento de dependência de dados

entre instruções de load e store;

A figura a seguir mostra um diagrama de blocos de

um estrutura típica de uma arquitetura superescalar.

Busca e Decodificação A arquitetura superescalar só é efetiva se a taxa média com que as instruções são buscadas e decodificadas for superior à taxa média com que instruções são executadas. Esquema eficiente de predição de desvios é fundamental. Necessidade de se dispor de um barramento de acesso ao cache de instruções com largura adequada e de um decodificador de instruções capaz de decodificar múltiplas instruções simultaneamente. Um decodificador de múltiplas instruções demanda a realização da busca de vários operandos em paralelo o banco de registradores com múltiplas portas de leitura. Degradação do Desempenho da Operação de Busca de Instruções Falha no acesso à cache de instruções: Bem mais do que um ciclo é gasto para a busca do próximo conjunto de instruções. Predição errada de desvios: As instruções buscadas antecipadamente mostram-se inúteis e novas instruções terão que ser buscadas. Alternativa possível: busca simultânea de instruções de dois ou mais caminhos possíveis do código a cada desvio condicional aumento no custo de hardware (cache de instruções com múltiplas portas de acesso). Degradação do Desempenho da Operação de Busca de Instruções Desalinhamento do endereço das instruções alvo de um desvio em relação ao início de um bloco de cache: Menos instruções úteis são efetivamente buscadas “slots” de decodificação podem ficar subtilizados se a unidade de busca não for capaz de realinhar as instruções antes de passá-las à unidade de decodificação.

Arquitetura Superescalar

Na arquitetura superescalar, várias instruções podem ser iniciadas simultaneamente e executadas independentemente umas das outras. A arquitetura pipeline permite que diversas instruções sejam executadas ao mesmo tempo, desde que estejam em estágios diferentes do pipeline.

As arquiteturas superescalares incluem todos os aspectos do pipeline e ainda acrescentam o fato de as instruções poderem estar executando no mesmo estágio do pipelining (em linhas pipelining diferentes). Assim, elas têm a habilidade de iniciarem múltiplas instruções no mesmo ciclo de clock. A forma como estão dispostas e utilizadas as estruturas e os componentes do processador define o modelo da arquitetura de um processador. Há diversas classificações de arquiteturas de processadores baseadas nas suas políticas e nos caminhos de execução dos dados.

Uma arquitetura superescalar deve possuir uma série de componentes especiais para executar mais de uma instrução por ciclo:

Unidade de Busca de Instruções: capaz de buscar mais de uma instrução por ciclo. Possui também um preditor de desvios, que deve ter alta taxa de acerto, para poder buscar as instruções sem ter que esperar pelo resultados dos desvios. Unidade de Decodificação: capaz de ler vários operandos do banco de registradores a cada ciclo. Note que cada instrução sendo decodificada pode ler até dois operandos do banco de registradores. Unidades Funcionais Inteiras e de Ponto Flutuante: em número suficiente para executar as diversas instruções buscadas e decodificadas a cada ciclo. Superescalar x superpipeline Uma técnica alternativa para atingir alta performance no processamento é intitulada como superpipelined - termo utilizado pela primeira vez em 1988. Essa técnica explora o fato de que o estágio de pipeline executa tarefas que requerem menos de meio ciclo de clock. Assim, um processador com velocidade de clock interno dobrada, permite um aumento de performance de duas tarefas executadas em um único ciclo de clock externo.

Por exemplo: Uma máquina usando pipeline básico executa uma instrução por ciclo de clock e tem e um estágio de pipeline por clock também. O pipeline tem quatro estágios: busca, decodificação, execução e armazenamento do resultado. Ainda que várias instruções sejam executadas concorrentemente, apenas uma instrução encontra-se na fase de execução.

A implementação superpipelined é capaz de executar duas fases da pipeline de cada vez. Um forma alternativa de observa-lo passa por perceber que as instruções

executadas em cada fase podem ser divididas em duas partes, não sobrepostas, onde cada fase é executada em meio ciclo de clock. Uma implementação superpipelined com este comportamento denomina-se de grau 2. Esta imagem retrata bem as diferenças entre as duas implementações mencionadas.

A implementação superescalar pode executar duas instruções em paralelo, devido ao facto de existirem duas fases homólogas.

Ambas as implementações possuem o mesmo número de instruções executadas ao mesmo tempo, no mesmo estado.

Limitações A abordagem superescalar depende da habilidade de executar várias instruções em paralelo. O termo paralelismo no nível de instruções diz respeito ao nível no qual as instruções de um programa podem ser executadas de forma paralela (em média).

Dependência de dados verdadeira (true data dependency) Considere a seguinte seqüência de instruções:

add r1, r2 # carregar registrador r1 com a soma dos conteúdos de r1 e r2 move r1, r3 # carregar registrador r3 com o conteúdo de r1

A segunda instrução pode ser buscada e decodificada antecipadamente, mas não pode ser executada até que seja completada a execução da primeira instrução. A razão é que ela depende do dado produzido pela primeira. Essa situação é denominada como dependência de dados verdadeira (também chamada de dependência de fluxo ou dependência de escrita-leitura).

Dependência de desvios A presença de desvios condicionais em uma seqüência de instruções complica a operação do pipeline. A instrução seguinte a um desvio condicional (tomado ou não) depende dessa instrução de desvio. Esse tipo de dependência também afeta uma pipeline escalar, mas a conseqüência desse tipo de dependência é mais severa em uma pipeline superescalar, porque o número de instruções perdidas em cada atraso é maior. Se forem usadas instruções de tamanho variável, surge ainda um outro tipo de dependência. Como o tamanho de uma instrução particular não é conhecido, uma instrução deve ser decodificada, pelo menos parcialmente, antes que a instrução seguinte possa ser buscada. Isso impede a busca simultânea de instruções, requerida em uma pipeline superescalar. Essa é uma das razões pelas quais técnicas supersescalares são mais diretamente aplicáveis a arquiteturas RISC ou do tipo RISC, que possuem instruções de tamanho fixo.

Conflito de recursos Um conflito de recurso ocorre quando duas ou mais instruções competem, ao mesmo tempo, por um mesmo recurso. Exemplos de recursos incluem memórias, caches, barramentos, portas de bancos de registradores e unidades funcionais (por exemplo, o somador da ULA). Em termos de pipeline, um conflito de recurso apresenta um comportamento semelhante ao de uma dependência de dados. Existem, entretanto, algumas diferenças. Por um lado, conflitos de recursos podem ser superados pela duplicação de recursos, enquanto uma dependência de dados não pode ser eliminada. Além disso, quando uma operação efetuada em uma dada unidade funcional consome muito tempo para ser completada, é possível minimizar os conflitos de uso dessa unidade por meio de sua implementação como uma pipeline.

Sistemas paralelos

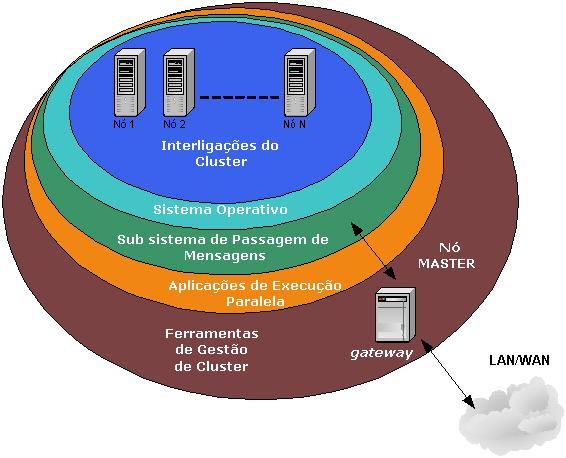

Um sistema de processamento distribuído ou paralelo é um sistema que interliga vários nós de processamento (computadores individuais, não necessariamente homogêneos), de maneira que um processo de grande consumo seja executado no nó "mais disponível", ou mesmo subdividido por vários nós.

Conseguindo-se, portanto, ganhos óbvios nestas soluções: uma tarefa qualquer, se divisível em várias subtarefas pode ser realizada em paralelo.

A nomenclatura geralmente utilizada neste contexto é HPC (High Performance Computing) e/ou DPC (Distributed/Parallel Computing).

Definição

Um sistema distribuído segundo a definição de Andrew Tanenbaum é uma "coleção de computadores independentes entre si que se apresenta ao usuário como um sistema único e coerente";[1] outra definição, de George Coulouris, diz: "coleção de computadores autônomos interligados através de uma rede de computadores e equipados com software que permita o compartilhamento dos recursos do sistema: hardware, software e dados"[carece de fontes].

Assim, a computação distribuída consiste em adicionar o poder computacional de diversos computadores interligados por uma rede de computadores. A união desses diversos computadores com o objetivo de compartilhar a execução de tarefas, é conhecida como sistema distribuído.

Organização Organizar a interação entre cada computador é primordial. Visando poder usar o maior número possível de máquinas e tipos de computadores, o protocolo ou canal de comunicação não pode conter ou usar nenhuma informação que possa não ser entendida por certas máquinas. Cuidados especiais também devem ser tomados para que as mensagens sejam entregues corretamente e que as mensagens inválidas sejam rejeitadas, caso contrário, levaria o sistema a cair ou até o resto da rede.

Outro fator de importância, é a habilidade de mandar softwares para outros computadores de uma maneira portável de tal forma que ele possa executar e interagir com a rede existente. Isso pode não ser possível ou prático quando usando hardware e recursos diferentes, onde cada caso deve ser tratado separadamente com cross-compiling ou reescrevendo software.

Modelos de computação distribuída Peer-to-peer (P2P) Ver artigo principal: Peer-to-peer Ponto-a-Ponto É uma arquitetura de sistemas distribuídos caracterizada pela descentralização das funções na rede, onde cada nó realiza tanto funções de servidor quanto de cliente.

Objetos distribuídos Semelhante ao peer-to-peer (do inglês peer-to-peer, que significa ponto-a-ponto) é um formato de rede de computadores em que a principal característica é descentralização das funções convencionais de rede, onde o computador de cada usuário conectado acaba por realizar funções de servidor e de cliente ao mesmo tempo.

Seu principal objetivo é a transmissão de arquivos e seu surgimento possibilitou o compartilhamento em massa de músicas e filmes. Com a crescente utilização da rede P2P para este fim, cada vez mais surgem programas para este fim, porém nem sempre eles atendem às expectativas do usuário.

Diversas redes operam hoje em dia nestes moldes de compartilhamento, entre elas Kademlia, Gnutela, Kad Network e SoulSeek. Alguns programas valem a pena ser citados quando o assunto é compartilhamento P2P: μTorrent, BitTorrent, SoulSeek, Ares Galaxy, Shareaza, DreaMule, iMesh e Morpheus. Caso prefira, acesse a categoria de Compartilhadores P2P do Baixaki e conheça mais programas que operam deste modo.

Mas com um Middleware intermediando o processo de comunicação.

Hardware A organização do hardware em sistemas com várias UCPs se dá por:

Sistemas paralelos Ver artigo principal: Sistema de processamento paralelo É constituído de vários processadores tipicamente homogêneos e localizados em um mesmo computador. Multicomputadores - Cada processador possui sua própria memória local. Multiprocessadores - Os processadores compartilham memória. Arquiteturas Multiprocessadores em barramento. Multiprocessador. Multiprocessador homogêneo. Multiprocessador heterogêneo. Software Fracamente acoplados - um software que serve de interface entre o computador (hardware) e os humanos (peopleware) , que permite a execução de diversos outros softwares (aplicativos).... Fortemente acoplados - permitem que máquinas e usuários de um sistema distribuído sejam fundamentalmente independentes e ainda interagir de forma limitada quando isto for necessário, compartilhando discos, impressoras e outros recursos. Sistemas operacionais Sistema operacional (SO) é um software que serve de interface entre o computador (hardware) e os humanos (peopleware) , que permite a execução de diversos outros softwares (aplicativos). SO de máquinas monoprocessadas. SO Multiprocessadores é uma extensão de SOs de máquinas monoprocessadas, a principal diferença sendo que os dados da memória são acessados por vários processadores e, portanto, necessitam de proteção com relação aos acessos concorrentes. SOs Multicomputadores são uma alternativas para o buffering de mensagens e pontos de bloqueio, alguns SOs disponibilizam uma abstração de memória compartilhada. SOs de rede: existe uma independência entre os computadores. Sistemas fortemente acoplados Neste sistema existe vários processadores compartilhando uma memória, e gerenciado por apenas um S.O.

Múltiplos processadores permitem que vários programas sejam executados ao mesmo tempo e em tempo real.Com isso será possível aumentar a capacidade de computação adicionando apenas processadores.

Exemplos os sistemas operacionais mais conhecidos hoje são: Windows, GNU/Linux, MacOS(Apple). Um exemplo clássico de computação distribuída é o projeto Seti at home que visa procurar em sinais de rádio interplanetários algum vestígio de vida extraterrestre. O exemplo mais moderno desse paradigma é o BOINC, que é um framework de grade computacional no qual diversos projetos podem rodar suas aplicações, como fazem os projetos World Community Grid, SETI@Home, ClimatePrediction.net, Einstein@Home, PrimeGrid e OurGrid.