Solução Exercícios Circuitos Aritméticos: mudanças entre as edições

imported>Fargoud Sem resumo de edição |

imported>Fargoud Sem resumo de edição |

||

| (3 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

1) | 1) Questão: | ||

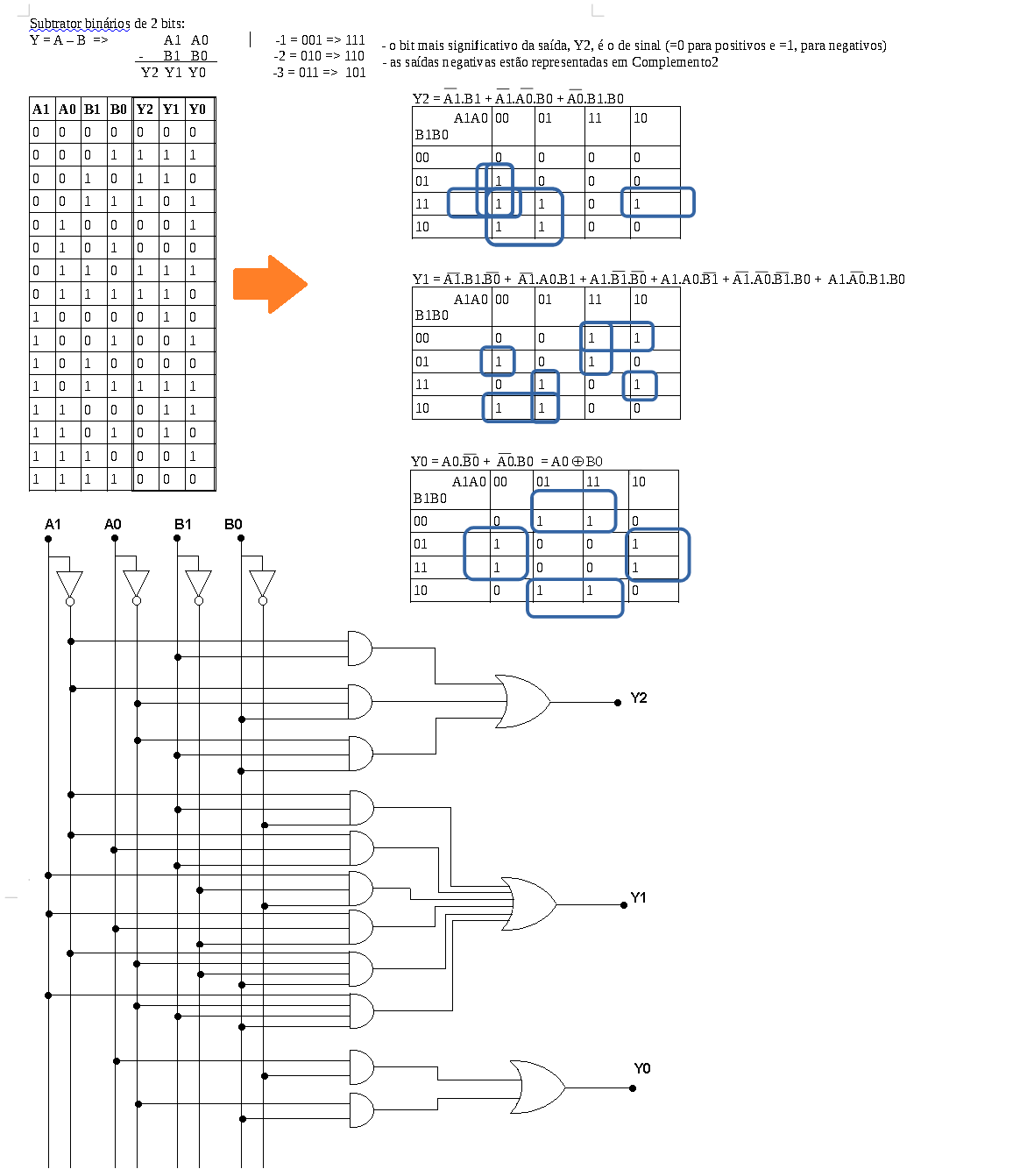

Elabore um módulo subtrator de 2 números binários de 2 bits, a partir da TV. | |||

[[image: ELDcaritex1.png|center]] | [[image: ELDcaritex1.png|center]] | ||

2) | ----------------- | ||

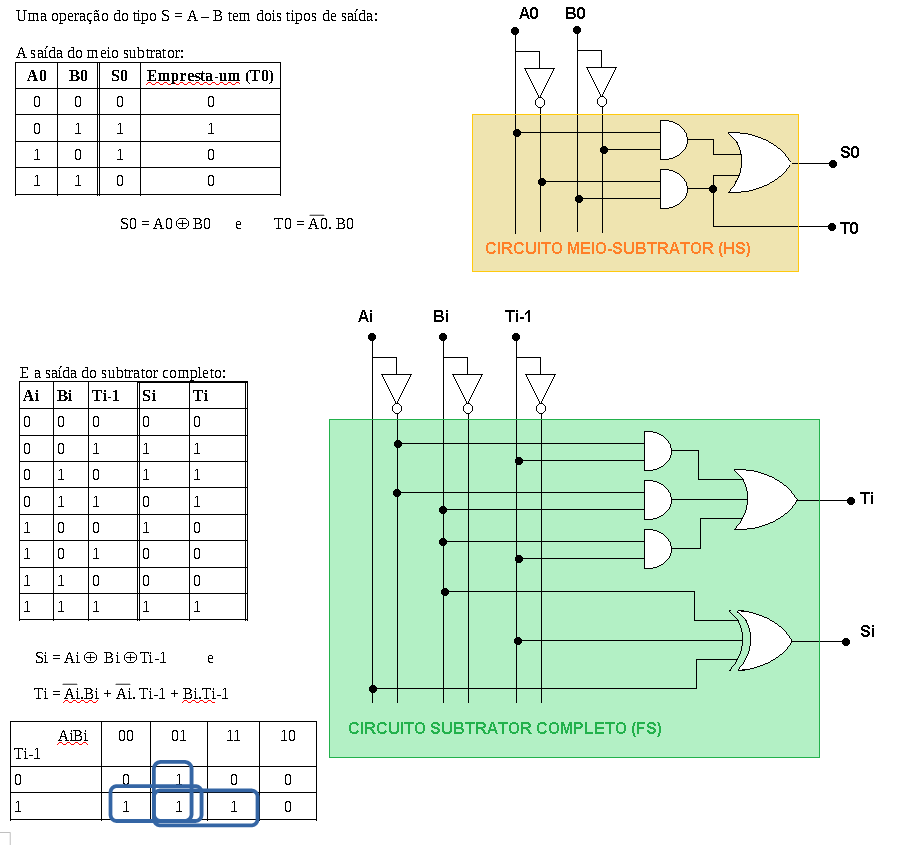

2) Questão: | |||

Elabore um módulo subtrator de 2 números binários de 4 bits, usando blocos de subtrator completo. | |||

[[image: ELDcaritex2.png|center]] | [[image: ELDcaritex2.png|center]] | ||

Então: | |||

[[image: ELDcaritex3.png|center]] | [[image: ELDcaritex3.png|center]] | ||

--------------- | |||

3) Questão: | |||

Elabore um módulo somador que efetue a adição de 3 números de 2 bits, usando blocos somadores completos e meio somadores. | |||

[[image: ELDcaritex3-2.png|center]] | |||

--------------- | |||

4) Questão: | |||

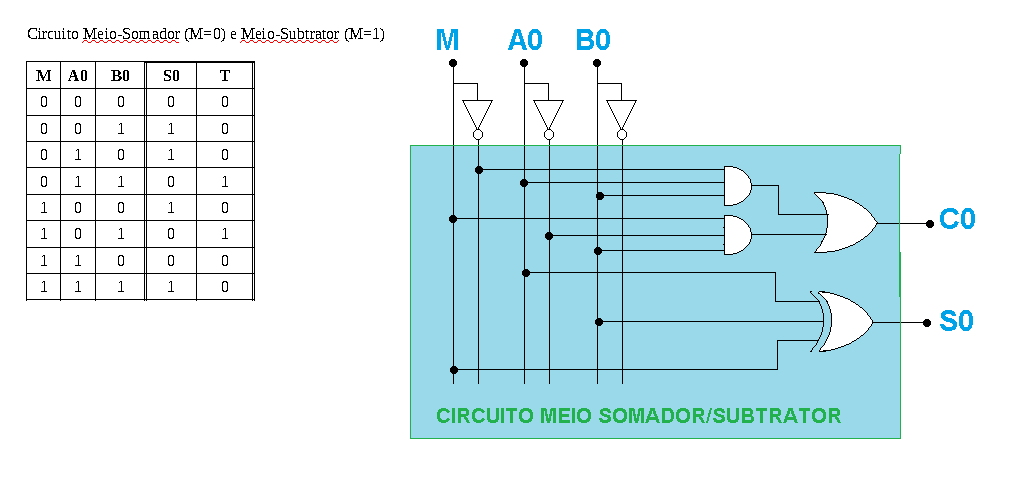

Projete um circuito lógico meio somador/meio subtrator. Adote: M=0 ⇒ meio somador M=1 ⇒ meio subtrator | |||

[[image: ELDcaritex4.png|center]] | [[image: ELDcaritex4.png|center]] | ||

--------------- | |||

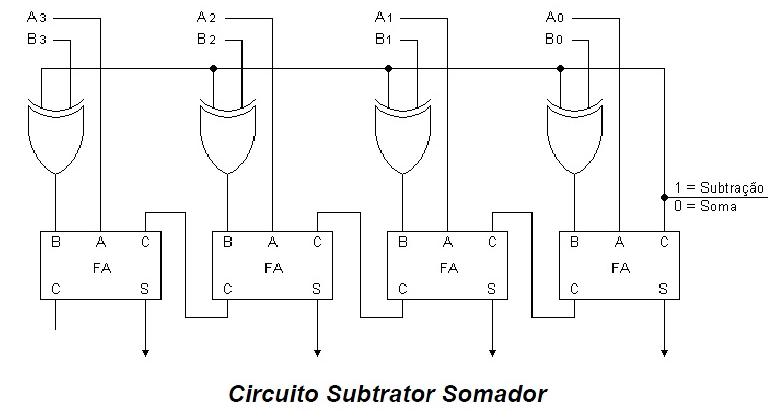

5) Esquematize, em blocos, um sistema somador/subtrator completo para 2 números de 4 bits. | |||

[[image: ELDcaritex5.png|center]] | [[image: ELDcaritex5.png|center]] | ||

--------------- | |||

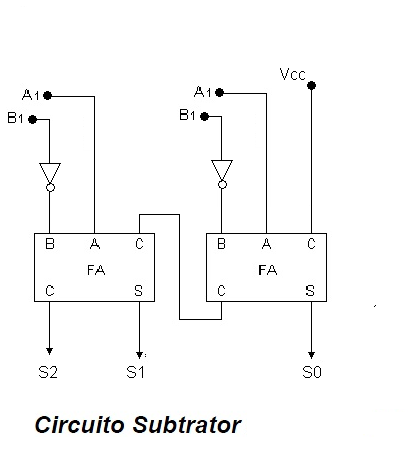

6) Utilizando blocos de somadores completos, elabore um sistema subtrator para 2 números de 2 bits. | |||

[[image: ELDcaritex6.png|center]] | |||

--------------- | |||

7) Obtenha um circuito somador completo usando 2 blocos meio somadores e porta lógica OU. | |||

[[image: ELDcaritex7.png|center]] | |||

--------------- | |||

8) Obtenha um circuito subtrator completo usando 2 blocos meio subtratores e porta lógica OU. | |||

[[image: ELDcaritex8.png|center]] | |||

--------------- | |||

9) Em um a ULA 74181, são estabelecidos para as entradas A3A2A1A0 = 1010 e B3B2B1B0 = 0111. Monte uma tabela com os valores a serem obtidos, simulando todas as entradas de controle Cn, M e S3S2S1S0 | |||

[[image: ELDcaritex9.png|center]] | |||

Edição atual tal como às 12h27min de 17 de maio de 2018

1) Questão: Elabore um módulo subtrator de 2 números binários de 2 bits, a partir da TV.

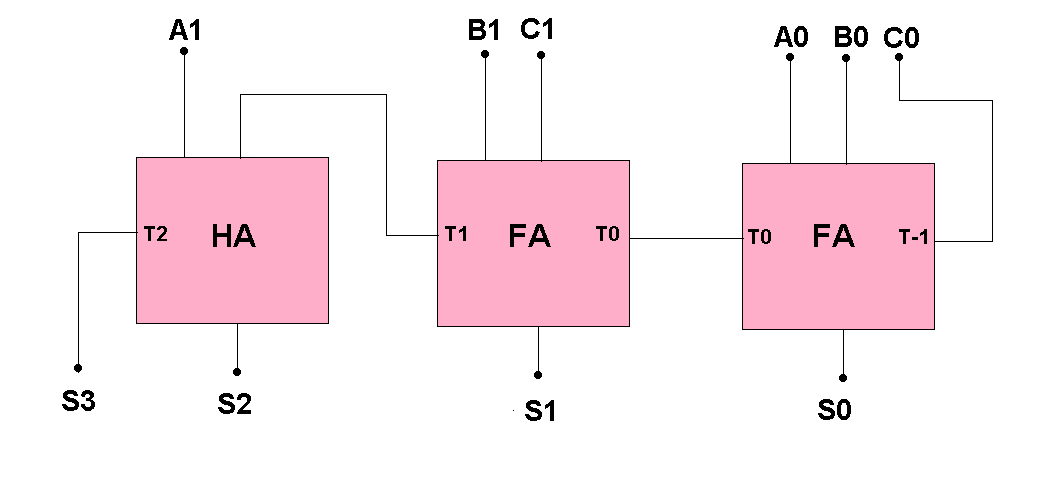

2) Questão: Elabore um módulo subtrator de 2 números binários de 4 bits, usando blocos de subtrator completo.

Então:

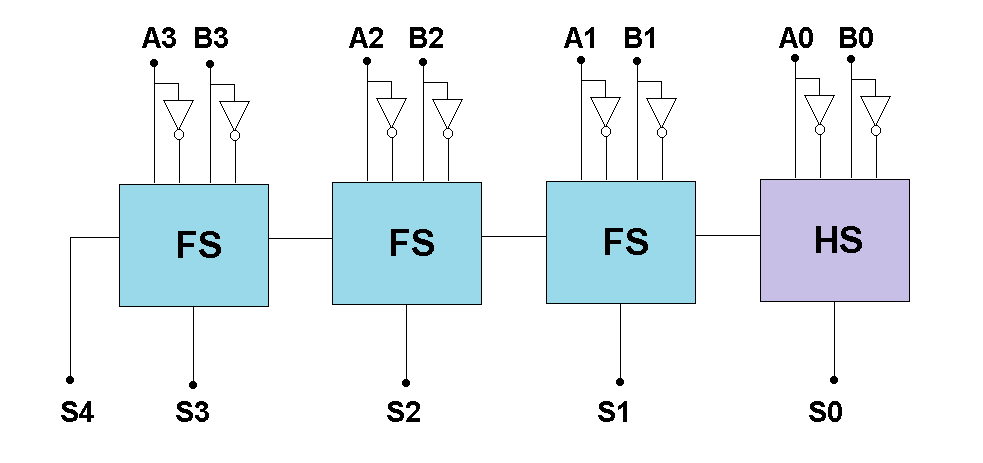

3) Questão: Elabore um módulo somador que efetue a adição de 3 números de 2 bits, usando blocos somadores completos e meio somadores.

4) Questão: Projete um circuito lógico meio somador/meio subtrator. Adote: M=0 ⇒ meio somador M=1 ⇒ meio subtrator

5) Esquematize, em blocos, um sistema somador/subtrator completo para 2 números de 4 bits.

6) Utilizando blocos de somadores completos, elabore um sistema subtrator para 2 números de 2 bits.

7) Obtenha um circuito somador completo usando 2 blocos meio somadores e porta lógica OU.

8) Obtenha um circuito subtrator completo usando 2 blocos meio subtratores e porta lógica OU.

9) Em um a ULA 74181, são estabelecidos para as entradas A3A2A1A0 = 1010 e B3B2B1B0 = 0111. Monte uma tabela com os valores a serem obtidos, simulando todas as entradas de controle Cn, M e S3S2S1S0