AULA 16 - Eletrônica Digital 1 - Graduação

Famílias Lógicas

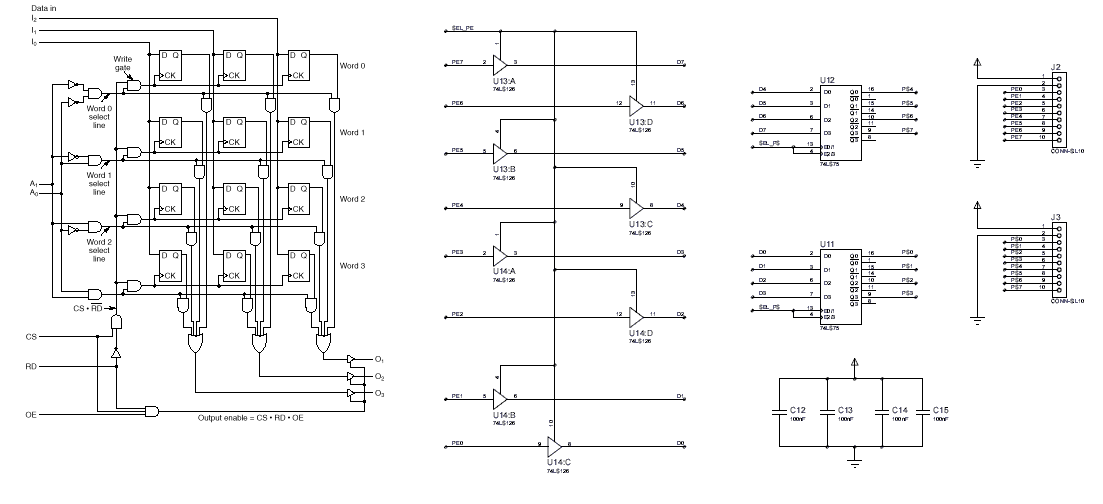

Este capítulo trata acerca dos aspectos construtivos e operacionais dos diferentes circuitos digitais lógicos, disponíveis comercialmente.

Histórico

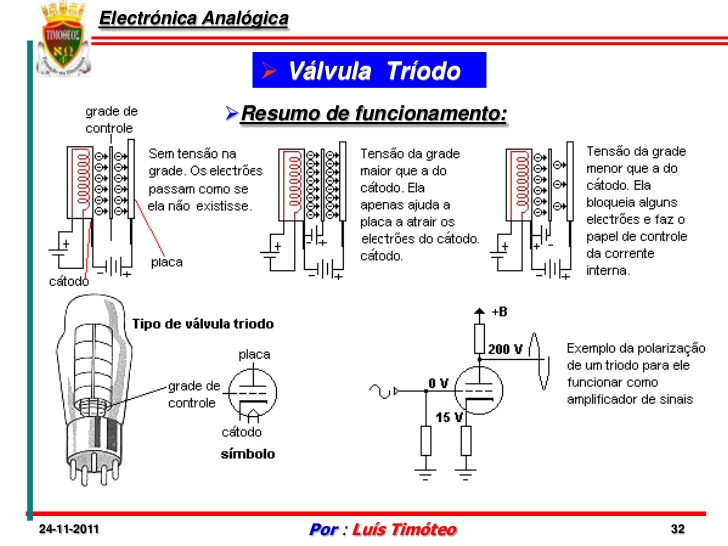

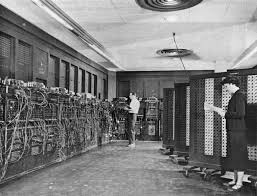

- Até 1955: diodos e válvulas

- Válvulas: grandes, alto consumo e geração de calor

- Transístor – consumo muito menor e dimensões muito reduzidas

- Com popularização do uso: “FAMÍLIAS” lógicas, para padronização dos níveis lógicos

Figura 1: Válvulas Eletrônicas

Figura 2: Computador ENIAC valvulado (1946)

Figura 3: Transístores

Principais Famílias Lógicas

- RTL – Lógica resistor-transistor

- DTL – Lógica diodo-transistor

- DCTL – Lógica transistor de acoplamento direto

- TTL – Lógica transistor-transistor

- ECL – Lógica emissor-acoplado

- MOS – Metal Oxide Semicondutor

- PMOS – Lógica MOSFETs de canal p

- NMOS – Lógica MOSFETs de canal n

- CMOS – Lógica MOSFETs complementares

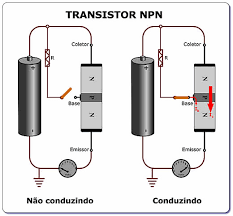

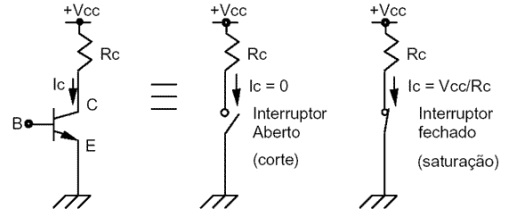

O transistor como chave

O transistor opera em 3 estados:

- CORTE – chave aberta → IB = 0

- Amplificação – conduzindo e amplificando a corrente da base → IB

- SATURAÇÃO – chave fechada → IB>>0

Figura 4: Funcionamento do transistor como chave

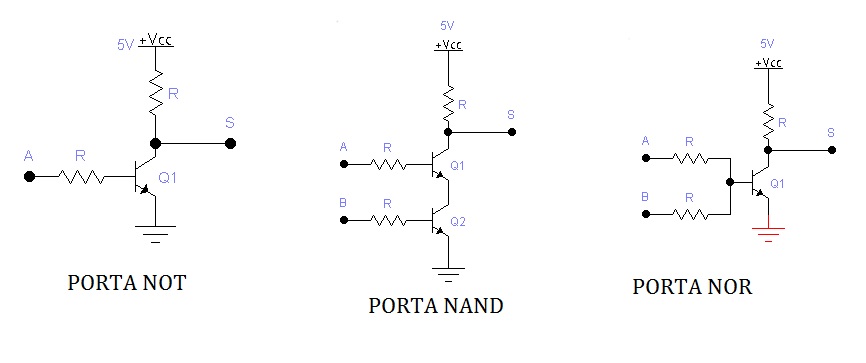

Gates básicos RTL

Figura 5: Portas tecnologia RTL

Apesar do sucesso, a família RTL trazia uma série de limitações, para criação de circuitos mais complexos.

Era necessário ter todos os componentes funcionando com a mesma tensão de alimentação, que fornecessem sinais que fossem reconhecidos pelos demais e sensíveis o suficiente para reconhecer os sinais dos demais.

Família TTL

Utilizam transistores bipolares como principal componente nos circuitos.

Desenvolvida pela Texas (TI) – família mais popular, durante um longo período.

Duas séries:

- 54 para uso militar - temperatura de operação [-55..125 graus Celsius]

- 74 para uso comercial - [0..70 graus Celsius]

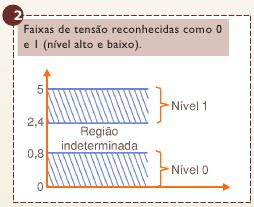

Níveis Lógicos de tensão:

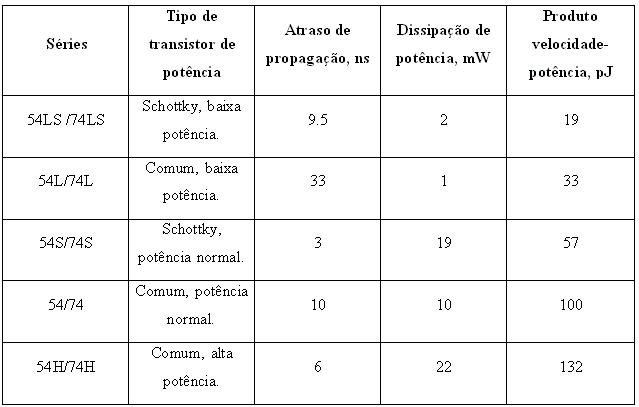

Classificação:

- SSI - Small Scale Integration ou Integração em Pequena Escala: 1 a 12 portas lógicas

- MSI - Medium Scale Integration ou Integração de Média Escala: 13 a 99 portas

- LSI - Large Scale Integration ou Integração em Grande Escala: 100 a 999 portas

- VLSI - Very Large Scale Integration ou Integração em Escala Muito Grande: mais de 1000 portas ou funções lógicas em um único CI.

Valores típicos:

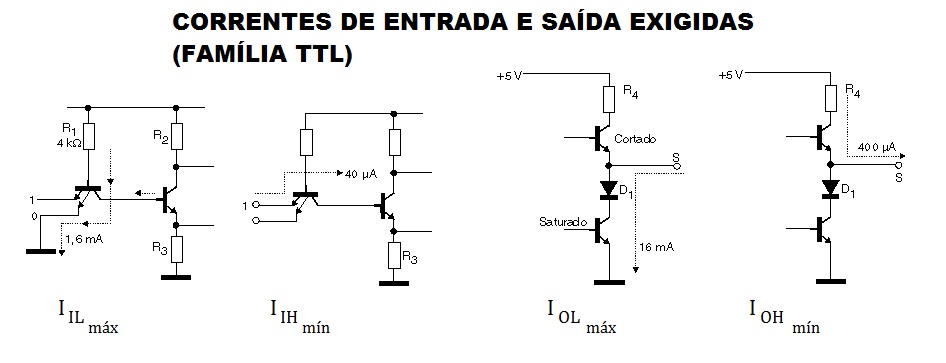

CORRENTES DE ENTRADA

- IIL máxima – corrente de entrada no CI TTL em nível lógico 0 – corrente saindo do CI da ordem de 1,6mA

- IIH mínima - corrente de Entrada no CI TTL em nível lógico 1 – corrente entrando no CI da ordem de 40 microA

CORRENTES DE SAÍDA

- IOL máxima – corrente de saída do CI TTL em nível lógico 0 – corrente drenada da ordem de 16mA

- IOH mínima - corrente de saída do CI TTL em nível lógico 1 – corrente fornecida da ordem de 400 microA

Pode-se então obter uma capacidade muito maior de excitação de saída de uma porta TTL quando ela é levada ao nível 0 do que ao nível 1!!

Por isto, às vezes quando ligamos um LED na saída, fazemos com que ele seja aceso quando a saída vai ao nível 0 (e portanto, a corrente é maior) e não ao nível 1 → normalmente ativo baixo ou anodo comum (AC)!!!

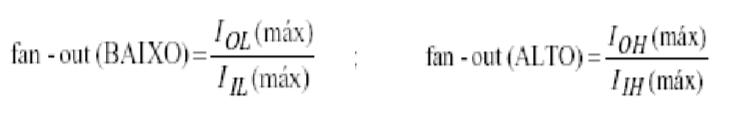

Fan-in e Fan-out

CAPACIDADE DE ENTRADA (fan-in): Fan-in é o número de entradas que uma porta lógica pode manipular.

Portas lógicas com valores grandes de fan-in tendem a ser mais lentas. Isto porque a complexidade do circuito de entrada aumenta a capacitância do dispositivo. No entanto, usar portas lógicas com maior fan-in ajuda a reduzir a profundidade dos circuitos lógicos.

CAPACIDADE DE SAÍDA (fan-out): A saída de um circuito lógico é projetada para alimentar várias entradas de outros circuitos lógicos.

O fan-out , também chamado fator de carga, é definido como o número máximo de entradas de circuitos lógicos que uma saída pode alimentar, de maneira confiável.

Exemplo 1: Uma porta lógica com fan-out de 10 pode alimentar até 10 entradas lógicas padrão.

Exemplo 1: Uma porta lógica com fan-out de 10 pode alimentar até 10 entradas lógicas padrão.

Para determinar quantas entradas diferentes a saída de um CI pode alimentar: IOL (máx) e IOH (máx) de tal CI e as necessidades de corrente de cada entrada, IIL e IIH:

Exemplo 2: Uma porta lógica com IOL máximo de 15 mA pode alimentar quantos CIs cuja IIL é de 0,7mA? Resposta: 21 CIs, porque o fan-out será dado por 15mA/0,7mA = 21,42.

Exemplo 3: Uma porta lógica com IOL máx de 16 mA e IOH mín de 320μA pode alimentar quantos CIs cujas IIL e IIH são de 1mA e 40μA, respectivamente? Resposta: Apenas 8 CIs, porque apesar de o fan-out para nível baixo ser de 16mA/1mA = 16 CIs, o fan-out para nível alto será limitado a 320μA / 40μA = 8 CIs.

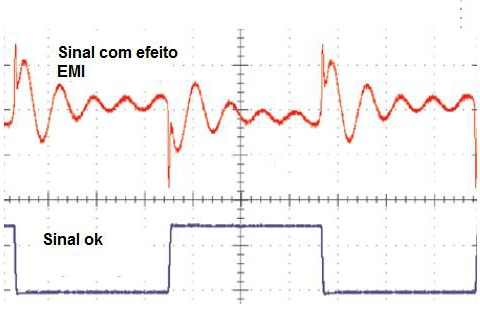

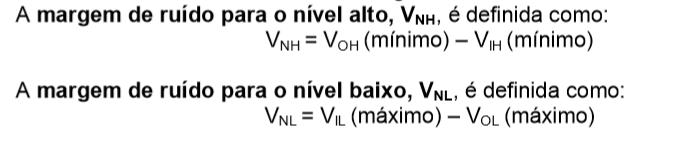

Margem de ruído:

As inúmeras fontes de interferência eletromagnética podem corromper totalmente o sinal digital:

Diferença entre tensões que permite que variações na alimentação e interferências não alterem os níveis lógicos:

Exemplo 4: Qual a margem de ruído de um CI com VOH de 3V, para alimentar um CI com VIH de 2V? Resposta: A margem será de 1V.

Exemplo 5: Qual a margem de ruído de um CI com VOL de 0,5V, para alimentar um CI com VIL de 0,8V? Resposta: A margem será de 0,3V.

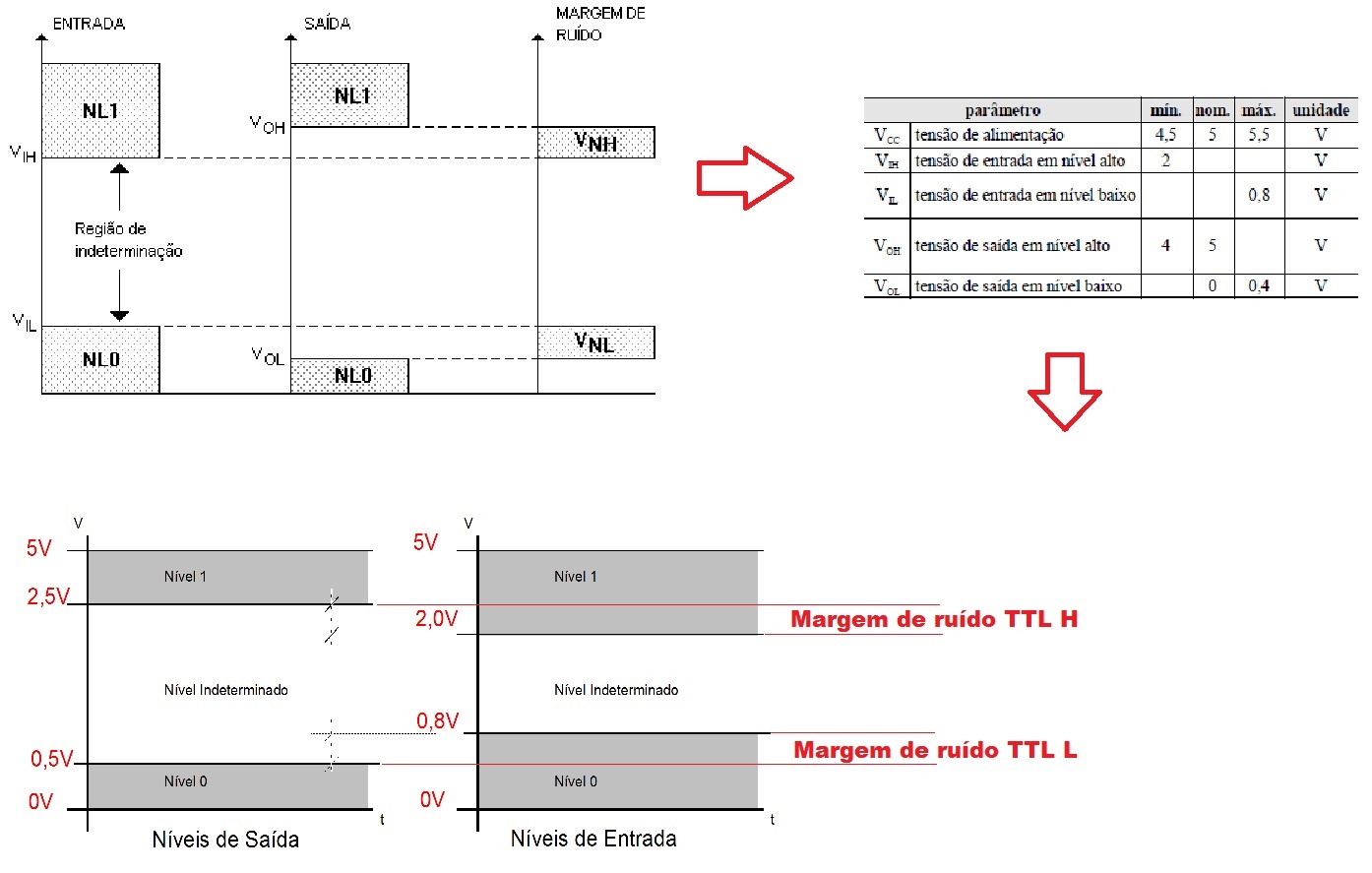

Entradas Flutuantes

Quando uma entrada ficar desconectada, a VI oscila no intervalo de 0,8 a 2,0 Volts -> a saída vai ficar variando aleatoriamente.

A isto chama-se “entrada flutuando” => Saída imprevisível!!!

O procedimento certo é o de b) (ou c) caso o fan-out permita):

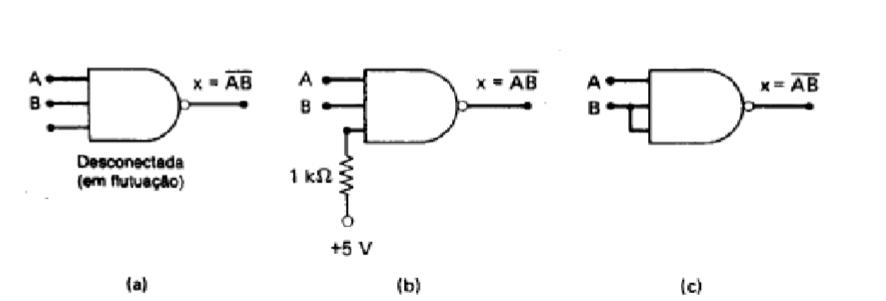

Velocidade

Dada pelo tempo que o sinal demora para propagar através do circuito.

Atraso entre o instante em que aplicamos os níveis lógicos na entrada e o instante em que obtemos a resposta.

Capacidade do transistor de mudar de estado mais rapidamente, quando mudar o estado das entradas.

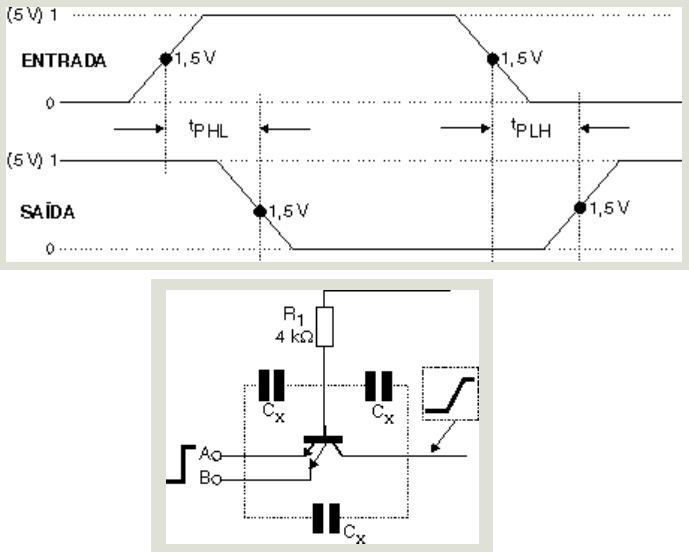

Formas de ligação:

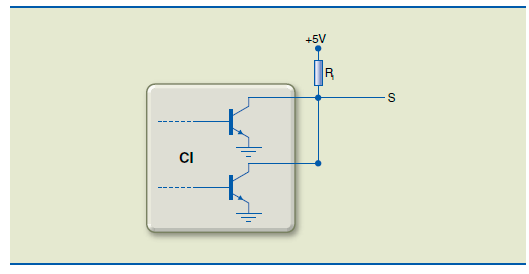

Saída em Coletor Aberto

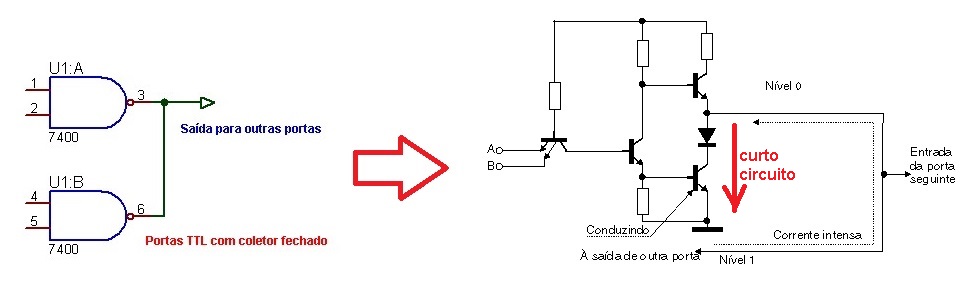

Até agora vimos CIs do tipo “Totem-Pole”, cujos terminais dos transistores internos (coletores ou emissores) são conectados fixamente a VCC ou GND, dependendo da função lógica.

Quando dois destes CIs forem ligados em paralelo e estiverem com saídas em níveis diferentes -> curto-circuito!

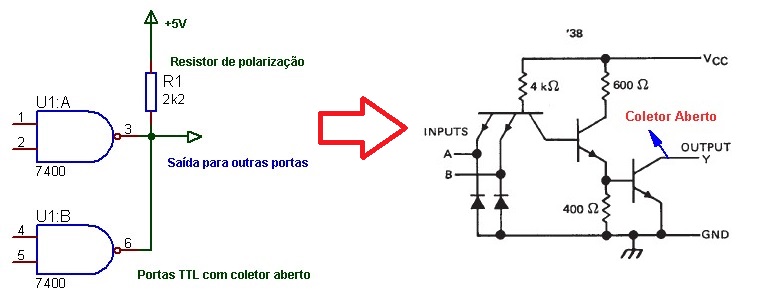

A alternativa são os CIs do tipo “Coletor Aberto”: o sinal de saída é aplicado à base de um transistor NPN interno, cujo coletor é exteriorizado (aberto) no pino do CI.

O emissor do transistor, por sua vez, é conectado internamente ao pino terra (GND).

Em outras palavras, em alguns CIs da família TTL o fabricante não completa o circuito internamente, deixando para que o projetista o complete externamente.

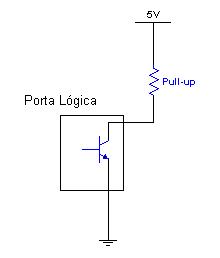

Para funcionar essa configuração, então, é necessária a instalação de um resistor externo ("pull-up") entre a saída (coletor do transitor interno) e o VCC.

Essa aparente desvantagem significa também que pode-se prescindir da tensão de +5V do VCC , podendo também utilizar +12V, por exemplo.

Se VF = 5 V (alimentação do CI), o valor usual para R é 2,2 kΩ.

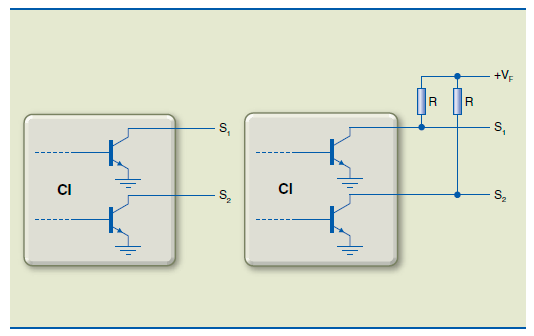

Os resistores R podem ser substituídos por um único resistor R1, conforme figura ao lado.

Esse procedimento coloca em curto as duas saídas sem gerar conflito, pois, se ambos os transistores estiverem

cortados ou saturados, seus coletores estarão no mesmo potencial e, portanto, o curto não trará problemas.

A saturação de um deles leva o coletor de ambos para “0” sem problema, devido ao resistor R1.

Além disto, esta configuração permite que se amplie o fan-out e que se implemente o que se chama de ligação E por fio (AND-wired), pois executa a função E, apenas com a ligação das saídas a um único resistor de pull-up, como acima.

Se as saídas não fossem coletor aberto, não poderiam ser conectadas, pois haveria conflito de tensões.

Nos circuitos integrados que utilizam tecnologia MOSFET, ao invés de transistores NPN, essa configuração é chamada de "dreno aberto" e funciona de forma semelhante.

O coletor aberto é um dos muitos padrões de entrada/saída digitais em uso hoje em dia.

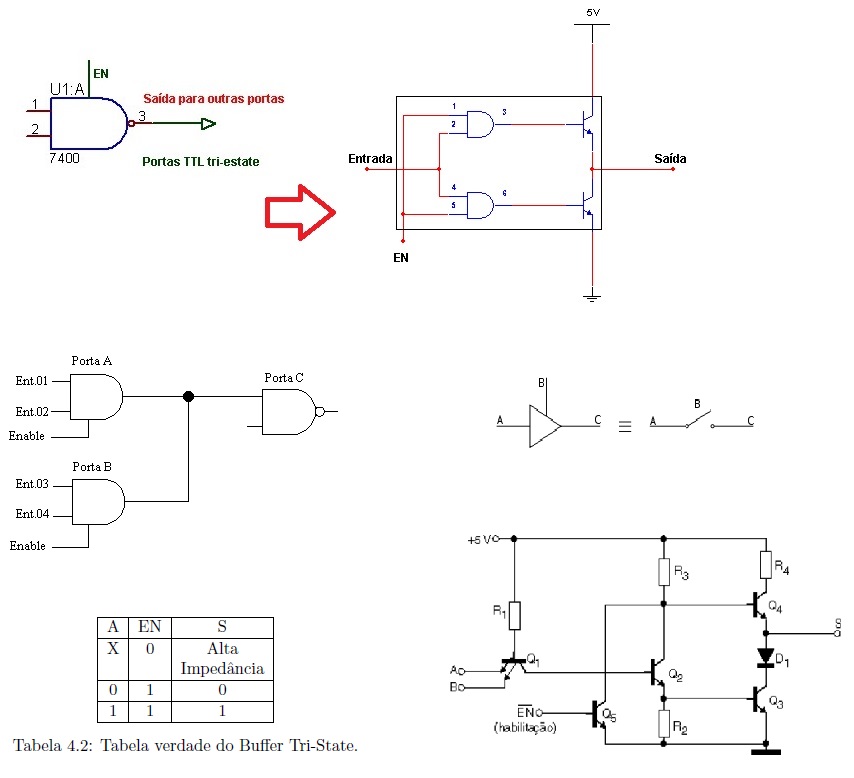

Saída em Tri-State

o “terceiro-estado” em um CI, quando sua saída comporta-se como circuito aberto, ou “alta impedância” (nem nível 0, nem 1).

Na prática, equivale a desconectar a saída do CI do circuito externo em que ela está conectada.

Os CIs TRI-STATE dispõem de uma entrada extra, chamada “Enable”, que habilita/desabilita a função no CI.

Esse recurso é interessante nos casos em que vários CIs compartilham o mesmo barramento, evitando conflito no envio dos dados.

Entrada em Schmitt trigger

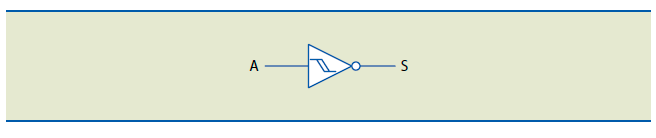

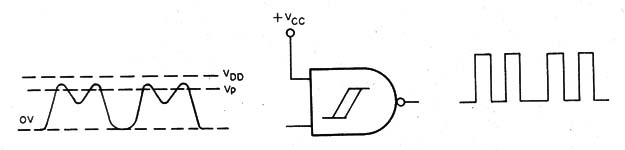

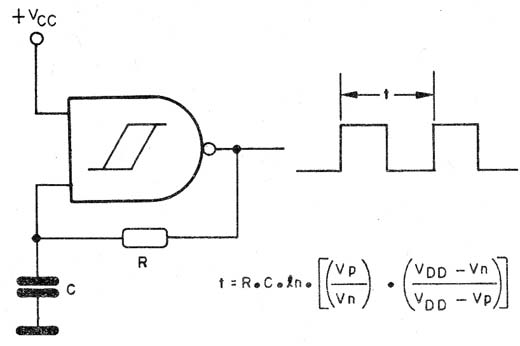

O símbolo da figura abaixo é de uma porta inversora com entrada Schmitt trigger (74HC14 ou 40106).

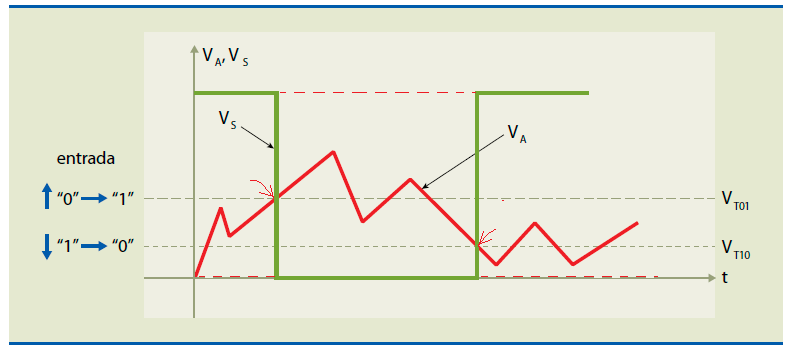

Schmitt trigger significa que a entrada tem dois valores diferentes para a transição lógica entre “0” e “1”: um para valores ascendentes da tensão de entrada e outro para valores descendentes da tensão de entrada.

O valor que resulta na transição de subida é maior que o valor que resulta na transição de descida.

Assim, uma entrada de tensão VA com ruído dentro de certos valores não apresentará mudança indesejável de estado na saída, desde que o valor de ruído não faça a entrada diminuir, ou aumentar para os valores de transição de comutação.

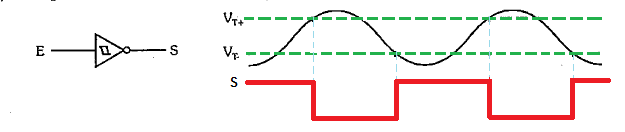

Se VA for uma tensão senoidal, obtemos uma onda quadrada com a mesma frequência da senoidal.

Outros exemplos de aplicação de um CI Schmitt Trigger ( 74132 - datasheet: media: ELDds74132.pdf, ou 4093):

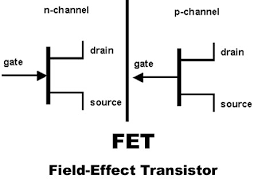

Família CMOS

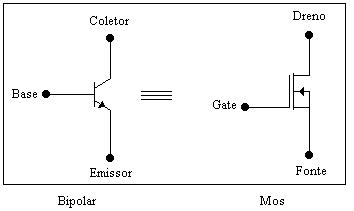

Utilizam os transistores unipolares MOSFET (transistor de efeito de campo construído segundo a técnica MOS - Metal Oxide Semicondutor), como seu elemento principal de circuito.

Atualmente é a tecnologia dominante no mercado, devido ao seu baixo custo e devido à grande densidade de portas lógicas que permite integrar por unidade de área. São utilizados em microprocessadores, microcontroladores e demais dispositivos eletrônicos de consumo.

Principal Família: série 4000.

Características:

As principais características desta família são:

- reduzido consumo de corrente (baixa potência);

- alta imunidade a ruídos;

- uma faixa de alimentação que se estende de 3V a 15V, ou 18V, dependendo do modelo

- processo de fabricação do CMOS mais simples que do TTL

- maior densidade de integração

- altíssima sensibilidade a eletricidade estática

- um pouco mais lentos do que os TTL, para tensões de alimentação baixas, apesar da nova série CMOS de alta velocidade competir em pé de igualdade com as séries TTL 74 e 74LS.

PRINCIPAIS CARACTERÍSTICAS:

TENSÃO DE SAÍDA (para VCC de 5 ou 10V) : VOL < 0,01V VOH ~ VCC

CORRENTE DE SAÍDA: para VCC de 5V: IOL ~ IOH ~ 1mA para VCC de 10V: IOL ~ IOH ~ 2,5mA

Séries:

A sub-famílias CMOS são:

- HC – High Speed CMOS – CMOS de Alta Velocidade

- HCT – High Speed CMOS with TTL inputs – CMOS de Alta Velocidade com entradas TTL

- AC – Advanced CMOS – CMOS de Alta Velocidade-versão avançada

- ACT – Advanced CMOS com TTL inputs – CMOS com entradas TTL-versão avançada

- BCT – BiCMOS Technology – Tecnologia BiCMOS (Bipolar/CMOS)

- ABT – Advanced BiCMOS Technology – Tecnologia BiCMOS Avançada

- LVT – Low Voltage Technology – Tecnologia de Baixa Tensão

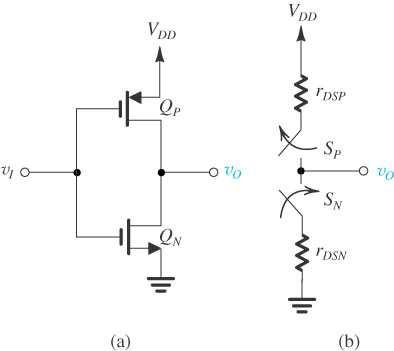

Gate inversor CMOS:

1) Sempre um dos transistores estará cortado, independente do sinal de entrada (H ou L) : corrente entre o Vdd e o Gnd → 0. Como na entrada a impedância é elevadíssima e praticamente nenhuma corrente circula → consumo da ordem de 10 nanowatt.

2) Como consequência pela configuração de transistores, cria-se uma “capacitância” que torna a mudança de estados na saída mais lenta.

Outras características:

CORRENTE DE FUGA NA ENTRADA: para VCC de 10V: IGS ~ 1pA

POTÊNCIA: corrente de alimentação Idd da ordem de 1 nA (típica) e 0,05 microA (máxima), para VCC de 5V -> ~5 nW ~10 nW, para VCC de 10V

VELOCIDADE: Atualmente a diferença de velocidade entre CMOS e TTL está sendo consideravelmente diminuída e depende fundamentalmente dos níveis de tensão e corrente utilizados.

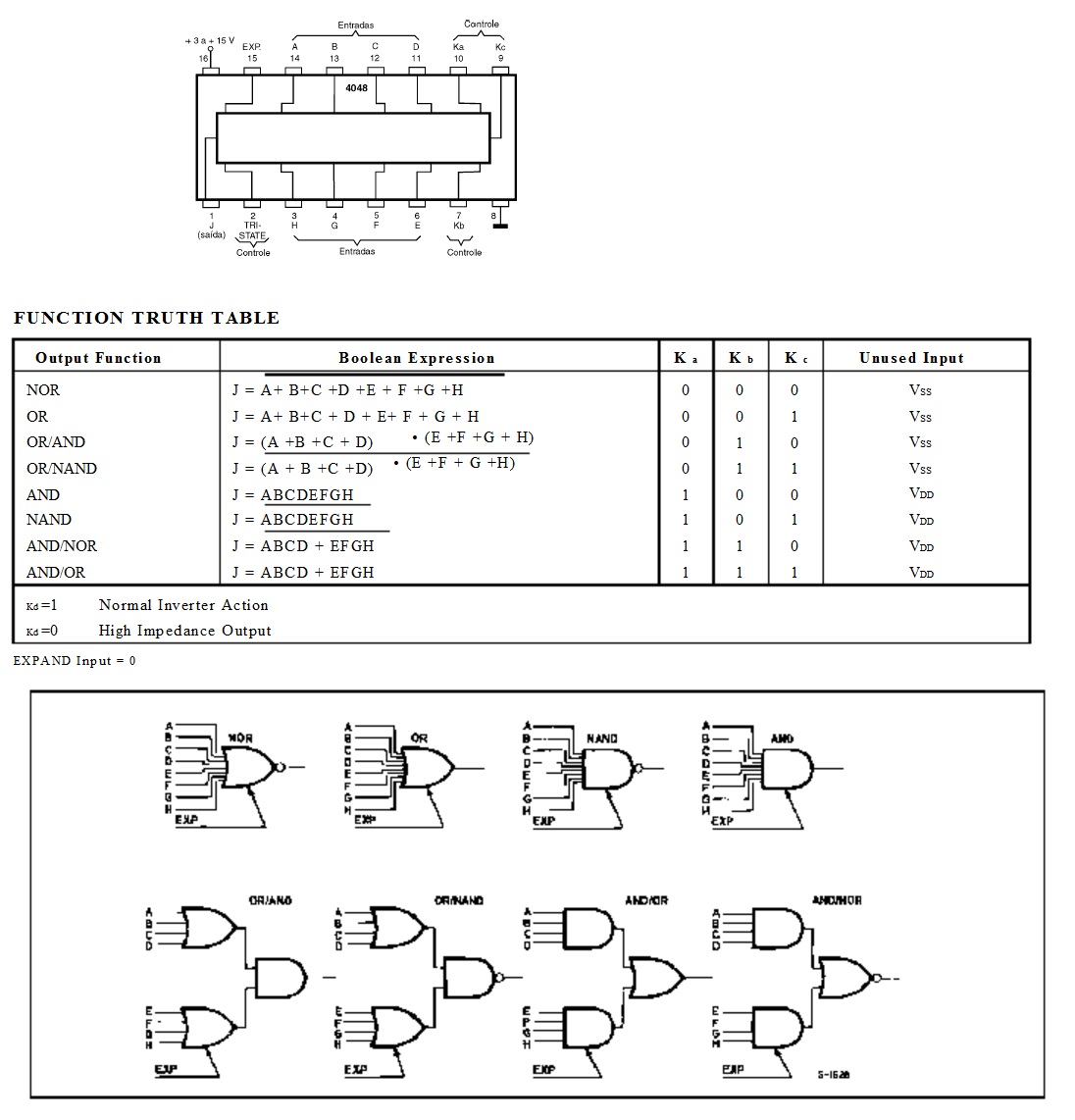

Função Tri-state do 4048:

Este circuito possui 8 entradas, uma saída e três entradas de "programação".

Dependendo dos níveis lógicos nas entradas de programação, o circuito de forma diferente:

Interfaceamento

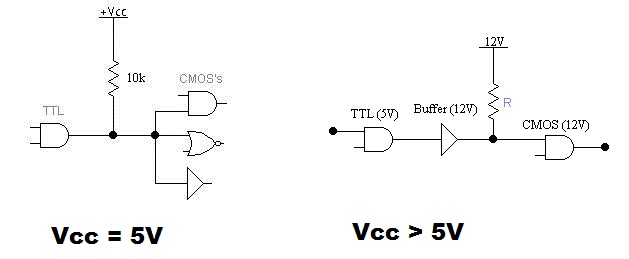

TTL excitando CMOS

Se VCC = 5 V -> interligação direta

Como as entradas CMOS têm uma impedância muito alta (não exigindo praticamente corrente alguma) da saída TTL, não existe perigo do circuito CMOS "carregar"a saída TTL.

Como VIH ≥ 3,5 V, para circuitos CMOS, enquanto que VOH ≥ 3,3 V no TTL -> Resistor externo de Pull-Up

Para garantir que a entrada CMOS reconheca o nível alto TTL

Se VCC > 5 V -> interligação direta

Deverá haver um circuito intermediário para casar as características.

Pode ser simplesmente um buffer não-inversor com coletor aberto e resistor de pull-up (para a tensão Vcc do CMOS):

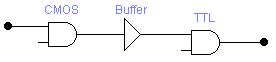

CMOS excitando TTL

Como no CMOS: IOH ~ IOL ~ 0,5 mA e no TTL: IIL = 1,6 mA => CMOS não suporta esta corrente

Intercalar ambos com buffer (ex., 4049 e 4050):

Mais sobre os componentes da família CMOS: [Newton C. Braga]

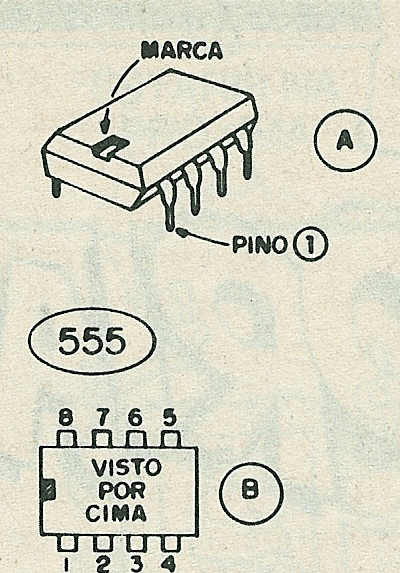

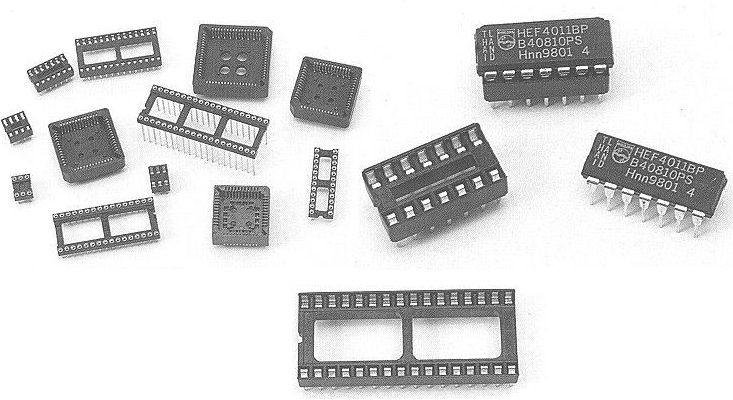

Encapsulamento

Os principais tipos de cápsulas utilizadas para envolver e proteger os chips são basicamente quatro:

- Cápsulas com dupla fila de pinos (DIL ou DIP – Dual In Line)

- Cápsulas planas (Flat-pack)

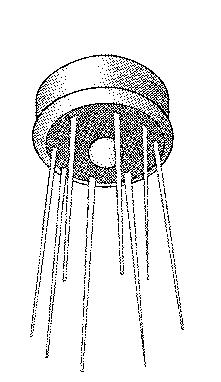

- Cápsulas metálicas TO-5 (cilíndricas)

- Cápsulas especiais

Enquanto as cápsulas TO-5 são de material metálico, as restantes podem utilizar materiais plásticos ou cerâmicos.

Cápsula com dupla fila de pinos

Para os CI de baixa potência – DIL ou DIP

As cápsulas de dupla fila de pinos são as mais utilizadas, podendo conter vários chips interligados.

Nos integrados de encapsulamento DIL a numeração dos terminais é feita a partir do terminal 1 (identificado pela marca), vai por essa linha de terminais e volta pela outra (em sentido anti-horário). Durante essa identificação dos terminais o CI deve ser sempre observado por cima.

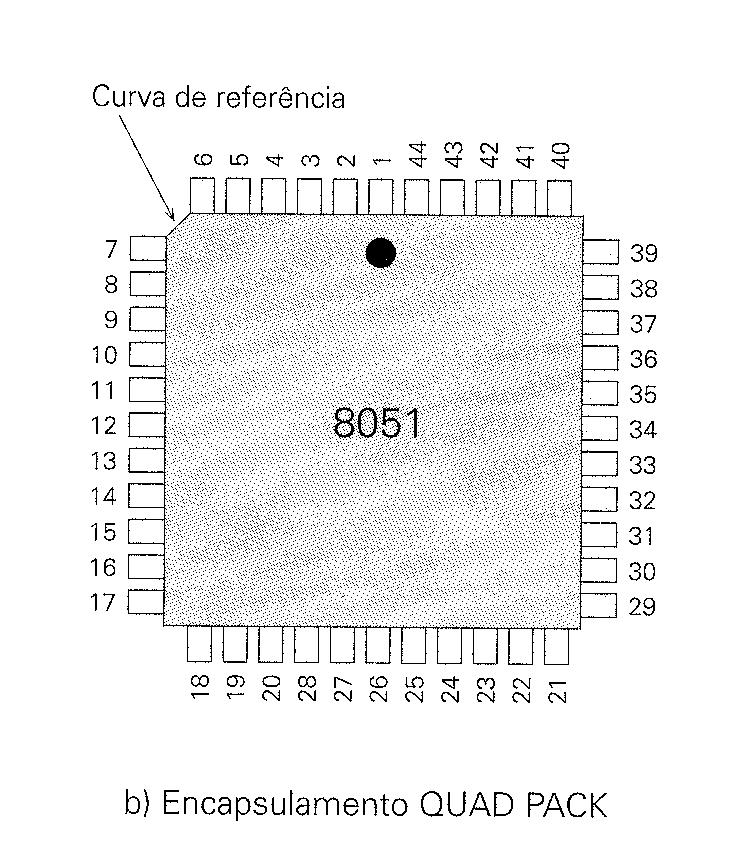

Cápsula com quatro filas de pinos

QIL – Quad In Line Para c.i. de média potência, por exemplo, amplificadores de áudio. A principal razão da linha quádrupla de pinos é o de permitir um maior afastamento das respectivas “ilhas” de ligação no circuito impresso, de forma que pistas mais largas (portanto para correntes maiores) possam ser ligadas a tais “ilhas”.

Cápsula com linha única de pinos

SIL – Single In Line Alguns integrados pré-amplificadores, e mesmo alguns amplificadores de certa potência, para áudio, apresentam esta configuração.

Flat-pack

As cápsulas planas têm reduzido volume e espessura e são formadas por terminais dispostos horizontalmente. Pelo facto de se disporem sobre o circuito impresso a sua instalação ocupa pouco espaço.

Cápsulas metálicas TO-5

Têm um corpo cilíndrico metálico, com os terminais dispostos em linha circular, na sua base.

A contagem dos terminais inicia-se pela pequena marca, em sentido horário, com o componente visto por baixo.

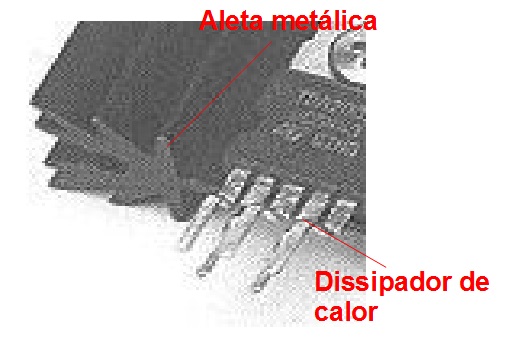

Cápsulas especiais

As cápsulas especiais são as que dispõem de numerosos terminais para interligarem a enorme integração de componentes que determinados chips dispõem (por exemplo, CI contendo microprocessadores).

Alguns integrados de potência têm uma cápsula extremamente parecida com a dos transístores de potência.

Algumas observações importantes a respeito das aletas de acoplamento aos dissipadores de calor:

- As aletas podem ser fixadas a dissipadores de alumínio em método idêntico ao utilizado nos transístores de potência.

- Acoplar-se as aletas à própria caixa (se for metálica) que contém o circuito.

- As aletas podem ser soldadas a uma das faces de cobre do circuito impresso (no caso de uma dupla face).

- As aletas, quase sempre estão ligadas eletricamente por dentro do c.i., ao pino correspondente ao negativo da alimentação (massa).

Tecnologia SMT

Existem três tipos básicos de cápsulas de circuitos integrados em SMT (Surface Mount Technology):

- SOIC – Small-Outline Integrated Circuit – é semelhante a um DIP em miniatura e com os pinos dobrados.

- PLCC – Plastic-Leaded Chip Carrier – tem os terminais dobrados para debaixo do corpo.

- LCCC – Leadless Ceramic Chip Carrier – não tem pinos. No seu lugar existem uns contactos metálicos moldados na cápsula cerâmica.

Soquetes

A base ou soquete, em termos práticos, além de facilitar a eventual manutenção do circuito, evita o aquecimento do circuito integrado quando se solda.

<<< Voltar para página principal do curso

| << Circuitos Aritméticos | AULA 16 - Famílias Lógicas | Flip-Flops >> |

|---|